### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# M32C/87 Group (M32C/87, M32C/87A, M32C/87B)

Hardware Manual RENESAS MCU M16C FAMILY / M32C/80 SERIES

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

### How to Use This Manual

### 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual.

The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the M32C/87 Group (M32C/87, M32C/87A, M32C/87B). Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Web site.

| Document Type    | Description                                         | Document Title         | Document No.  |

|------------------|-----------------------------------------------------|------------------------|---------------|

| Datasheet        | Hardware overview and electrical characteristics    | M32C/87 Group          | REJ03B0127-   |

|                  |                                                     | (M32C/87,              | 0151          |

|                  |                                                     | M32C/87A,              |               |

|                  |                                                     | M32C/87B)              |               |

|                  |                                                     | Datasheet              |               |

| Hardware manual  | Hardware specifications (pin assignments,           | M32C/87 Group          | This hardware |

|                  | memory maps, peripheral function                    | (M32C/87,              | manual        |

|                  | specifications, electrical characteristics, timing  | M32C/87A,              |               |

|                  | charts) and operation description                   | M32C/87B)              |               |

|                  | Note: Refer to the application notes for details on | Hardware Manual        |               |

|                  | using peripheral functions.                         |                        |               |

| Software manual  | Description of CPU instruction set                  | M32C/80 Series         | REJ09B0319-   |

|                  |                                                     | Software Manual        | 0100          |

| Application note | Information on using peripheral functions and       | Available from Renesas |               |

|                  | application examples                                | Technology Web site.   |               |

|                  | Sample programs                                     |                        |               |

|                  | Information on writing programs in assembly         |                        |               |

|                  | language and C                                      |                        |               |

| Renesas          | Product specifications, updates on documents,       |                        |               |

| technical update | etc.                                                |                        |               |

### 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

### (1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word "register," "bit," or "pin" to distinguish the three categories.

Examples the PM03 bit in the PM0 register

P3\_5 pin, VCC pin

### (2) Notation of Numbers

The indication "b" is appended to numeric values given in binary format. However, nothing is appended to the values of single bits. The indication "h" is appended to numeric values given in hexadecimal format. Nothing is appended to numeric values given in decimal format.

Examples Binary: 11b

Hexadecimal: EFA0h Decimal: 1234

### 3. Register Notation

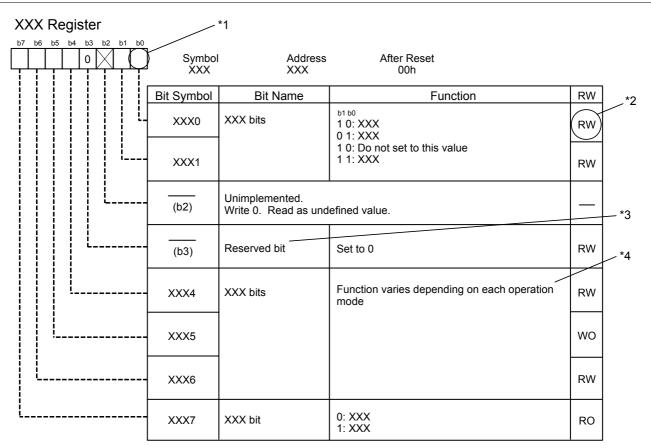

The symbols and terms used in register diagrams are described below.

\*1

Blank: Set to 0 or 1 according to the application.

0: Set to 0.

1: Set to 1.

X: Unimplemented.

\*2

RW: Read and write.

RO: Read only.

WO: Write only.

-: Unimplemented.

\*3

• Reserved bit

Reserved bit. Set to specified value.

\*4

• Unimplemented

Nothing is implemented to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information on the individual modes.

# 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connection                               |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SFR          | Special Function Registers                   |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

All trademarks and registered trademarks are the property of their respective owners. IEBus is a registered trademark of NEC Electronics Corporation.

# **Table of Contents**

| Specia | al Function Register (SFR) Page Reference                      | B - 1 |

|--------|----------------------------------------------------------------|-------|

| 1.     | Overview                                                       | 1     |

| 1.1    | Features                                                       | 1     |

| 1.1    | 1.1 Applications                                               | 1     |

| 1.1    | 1.2 Specifications                                             |       |

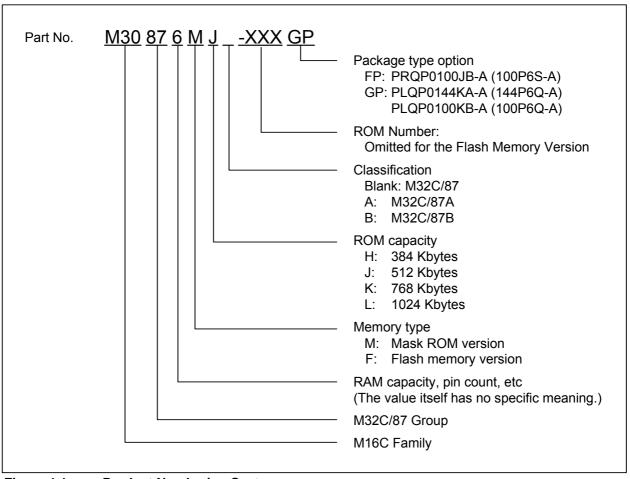

| 1.2    | Product List                                                   |       |

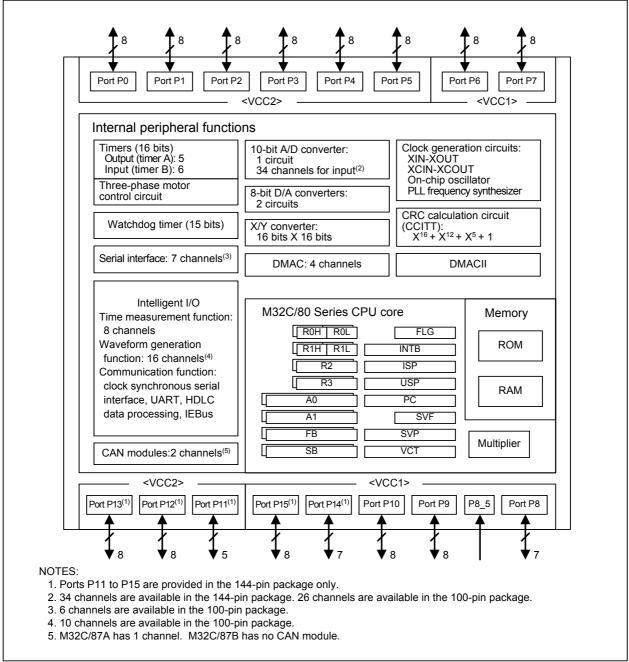

| 1.3    | Block Diagram                                                  | 8     |

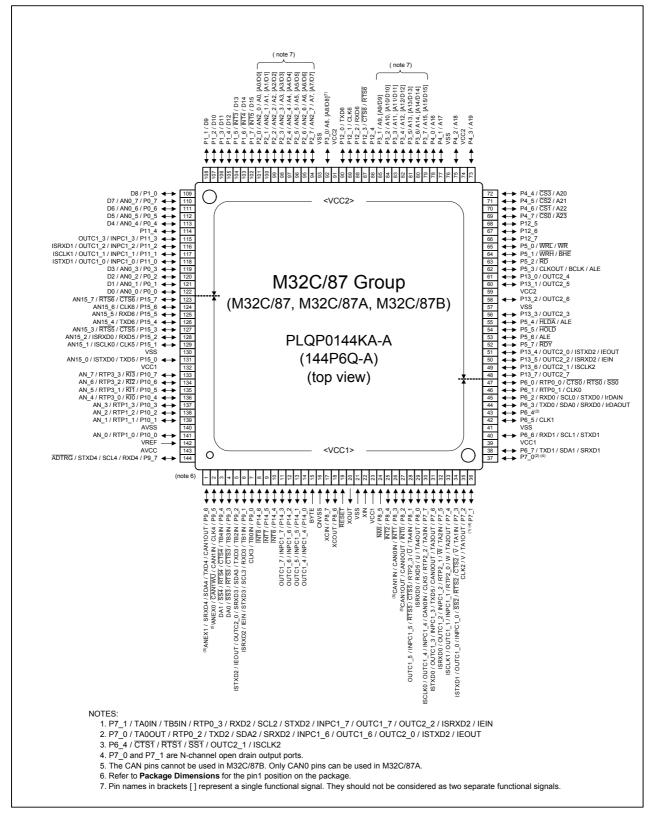

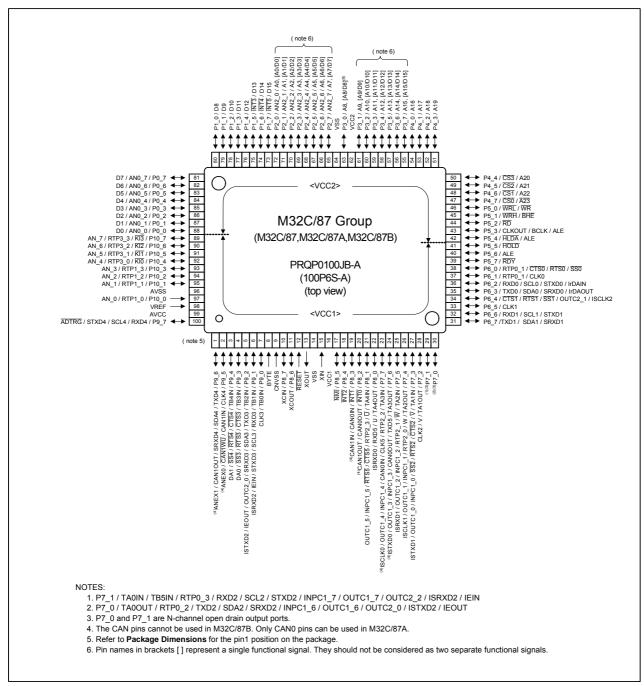

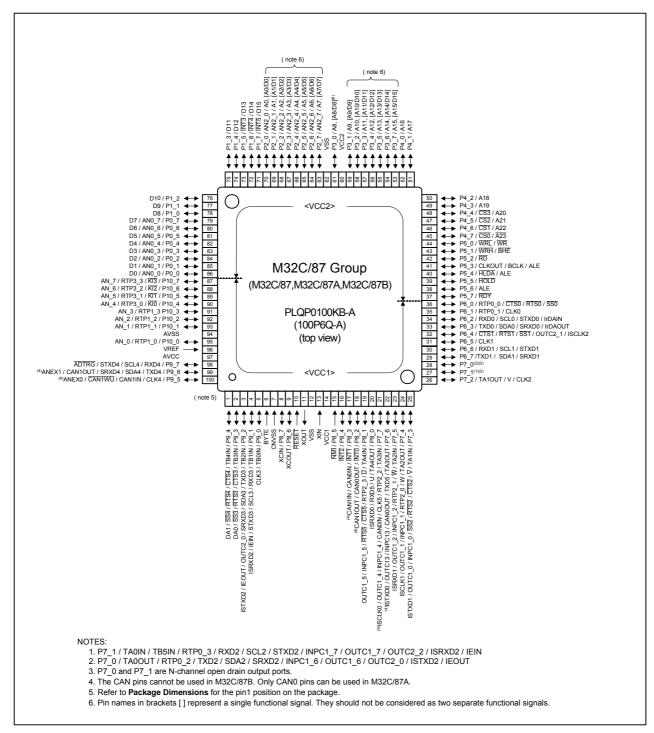

| 1.4    | Pin Assignments                                                | 9     |

| 1.5    | Pin Functions                                                  | 19    |

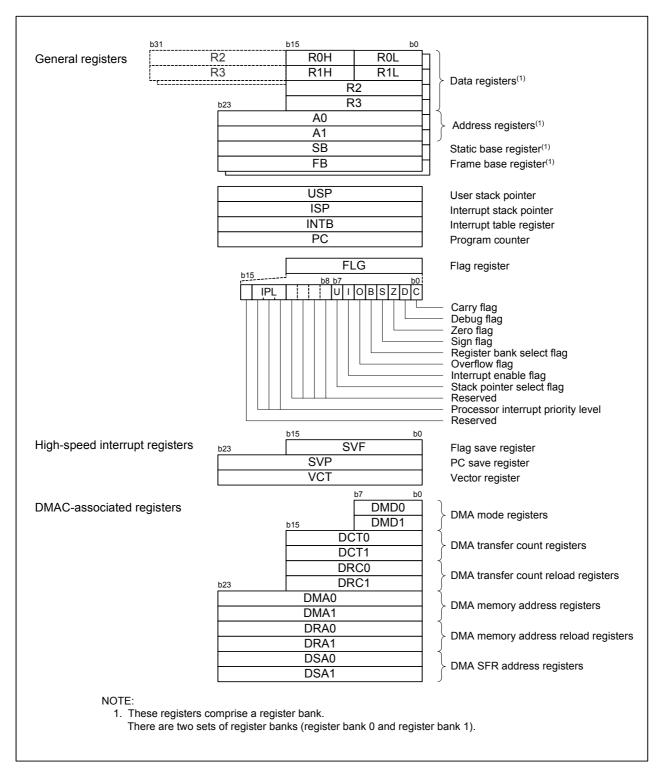

| 2.     | Central Processing Unit (CPU)                                  | 23    |

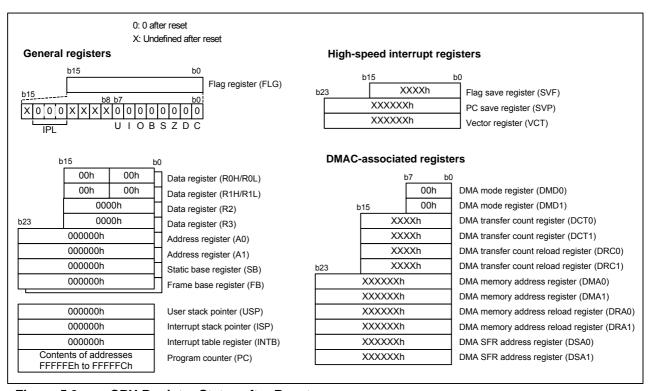

| 2.1    | General Registers                                              | 24    |

| 2.1    | 1.1 Data Registers (R0, R1, R2, and R3)                        | 24    |

| 2.1    | 1.2 Address Registers (A0 and A1)                              | 24    |

| 2.1    | 1.3 Static Base Register (SB)                                  | 24    |

| 2.1    | 1.4 Frame Base Register (FB)                                   | 24    |

| 2.1    | 1.5 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) | 24    |

| 2.1    | 1.6 Interrupt Table Register (INTB)                            | 24    |

| 2.1    | 1.7 Program Counter (PC)                                       | 24    |

| 2.1    | 1.8 Flag Register (FLG)                                        | 24    |

| 2.2    | High-Speed Interrupt Registers                                 | 25    |

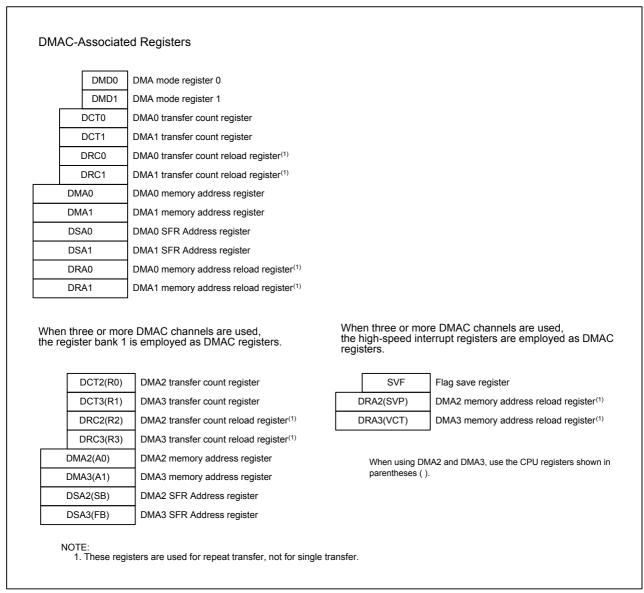

| 2.3    | DMAC-Associated Registers                                      | 25    |

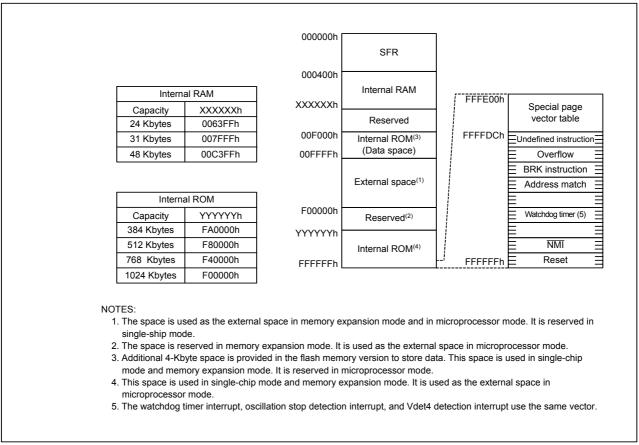

|        | Memory                                                         |       |

| 5.     | Reset                                                          | 47    |

| 5.1    | Hardware Reset 1                                               | 47    |

| 5.1    | 1.1 Reset at a Stable Supply Voltage                           |       |

| 5.1    | 1.2 Power-on Reset                                             |       |

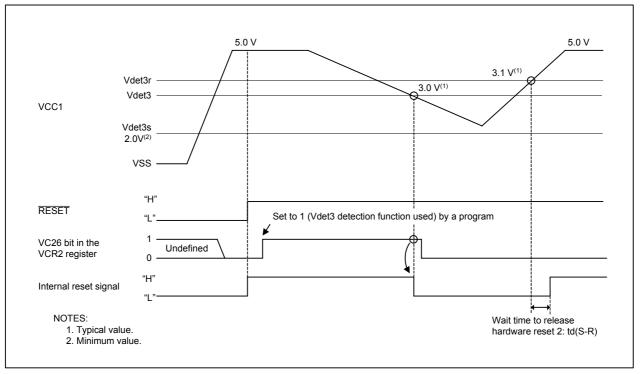

| 5.2    | Hardware Reset 2 (Vdet3 detection function)                    |       |

| 5.3    | Software Reset                                                 |       |

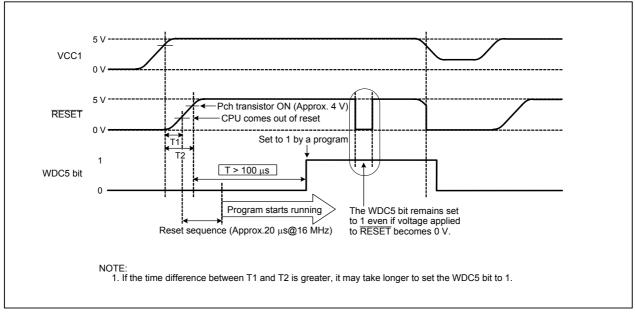

| 5.4    | Watchdog Timer Reset                                           | 49    |

| 5.5    | Internal Registers                                             | 50    |

| 6.     | Power Supply Voltage Detection Function                        | 51    |

| 6.1    | Vdet3 Detection Function                                       | 55    |

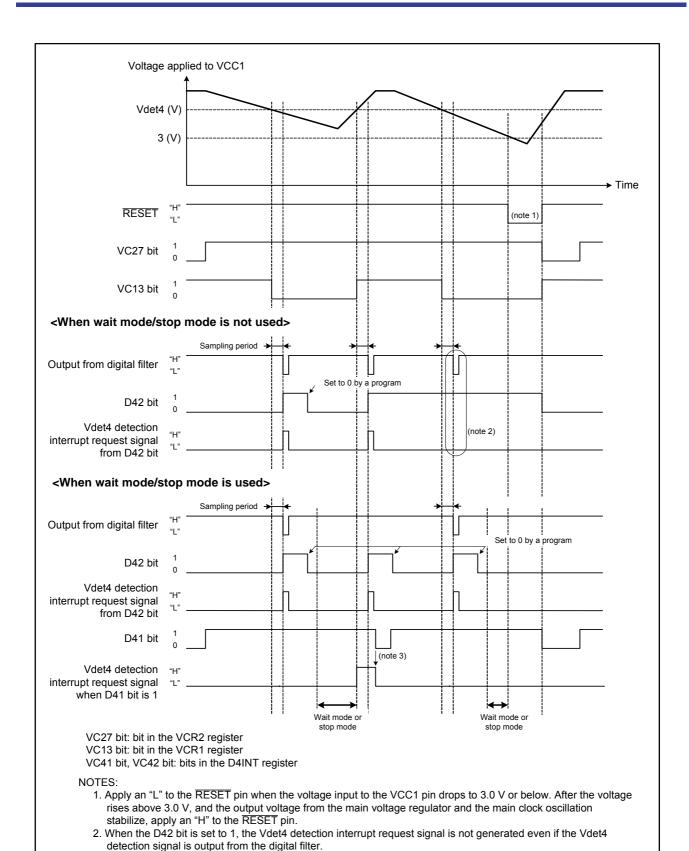

| 6.2    | Vdet4 Detection Function                                       | 56    |

| 6.2    | 2.1 Usage Notes on Vdet4 Detection Interrupt                   | 58    |

| 6.3    | Cold Start/Warm Start Determination Function                   | 58    |

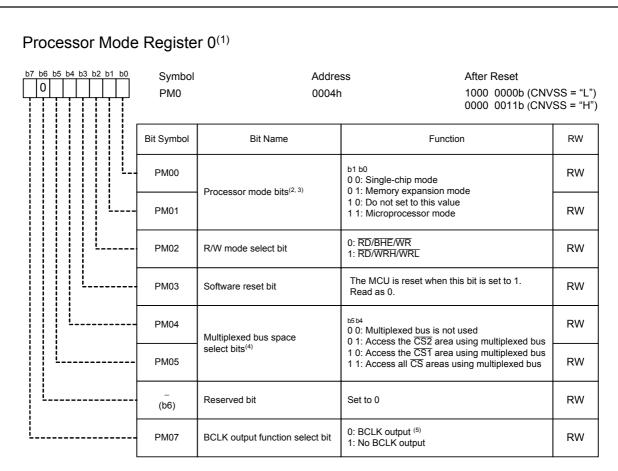

| 7.     | Processor Mode                                                 | 59    |

| 7.1    | Processor Mode                                                 | 59    |

| 7.2    | Setting of Processor Mode                                      |       |

| 8.     | Bus                                                            | 63    |

| 8.1    | Bus Settings                                                   | 63    |

| 8.1.1        | Selecting External Address Bus                         | 64  |

|--------------|--------------------------------------------------------|-----|

| 8.1.2        | Selecting External Data Bus                            | 64  |

| 8.1.3        | Selecting Separate Bus/Multiplexed Bus                 | 64  |

| 8.2          | Bus Control                                            |     |

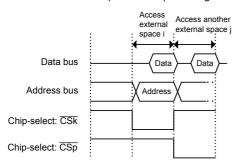

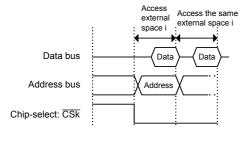

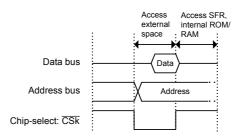

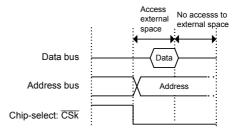

| 8.2.1        | Address Bus and Data Bus                               | 66  |

| 8.2.2        | Chip-Select Output                                     | 66  |

| 8.2.3        | Read/Write Output Signals                              |     |

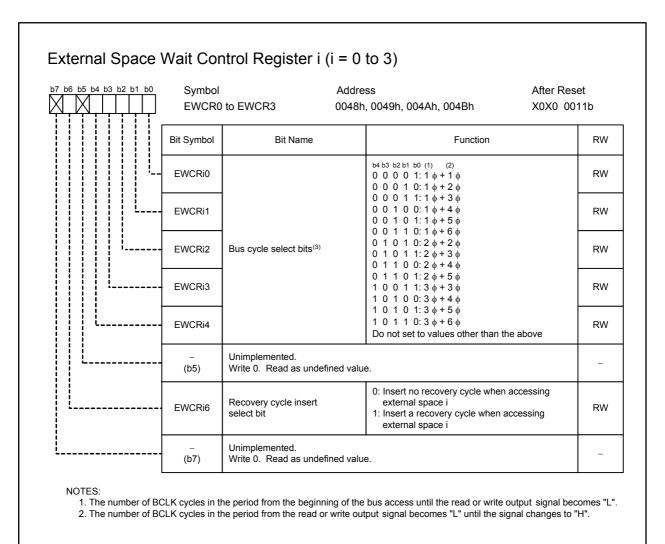

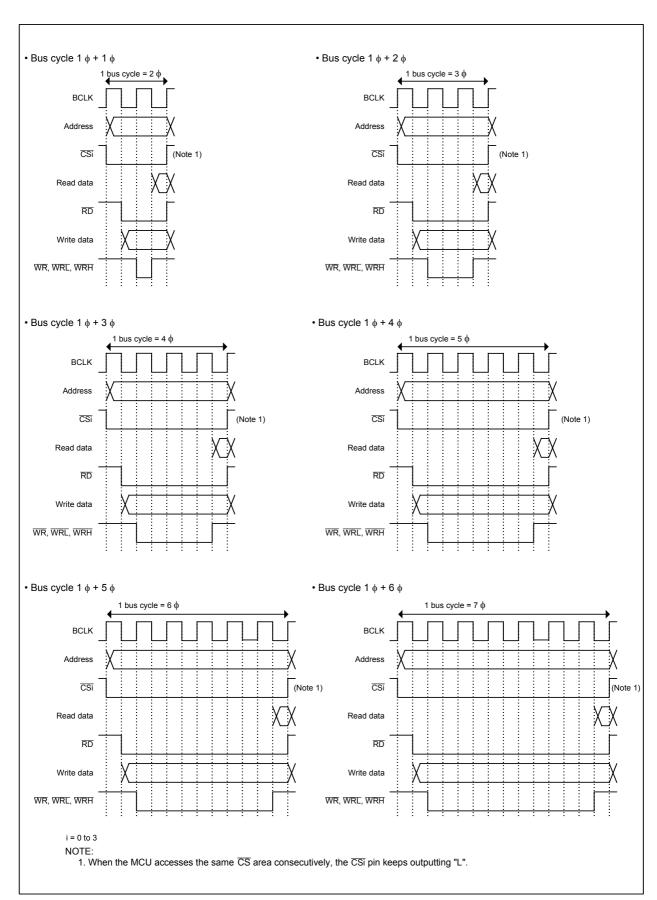

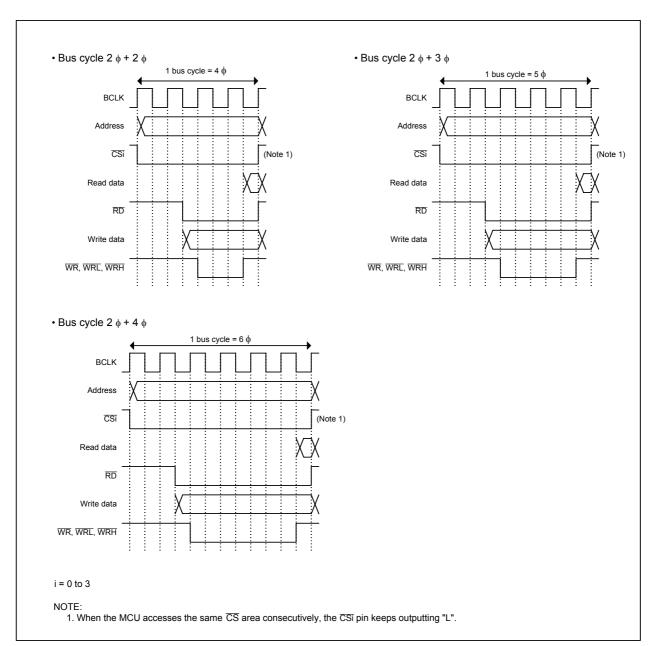

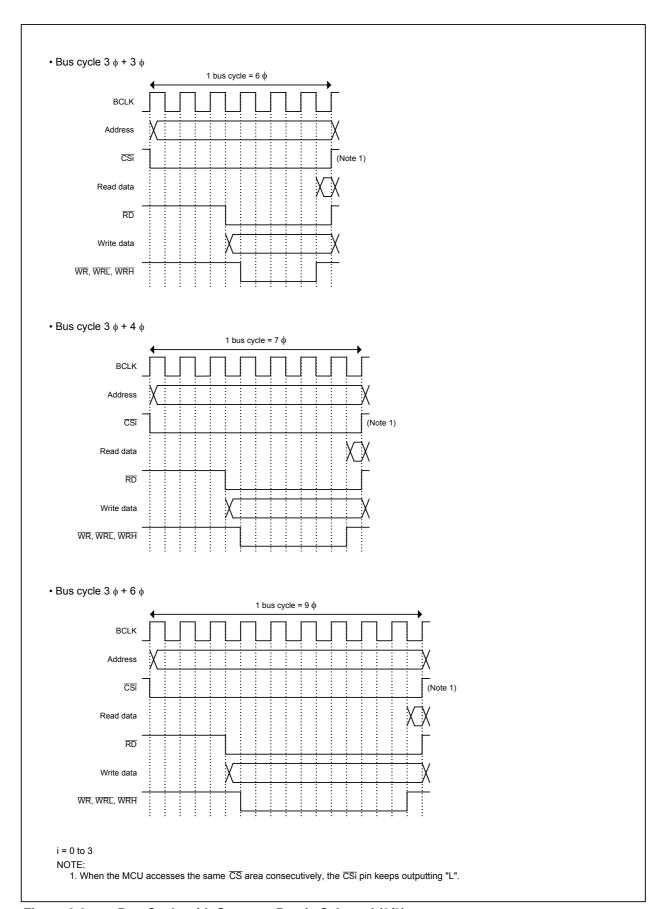

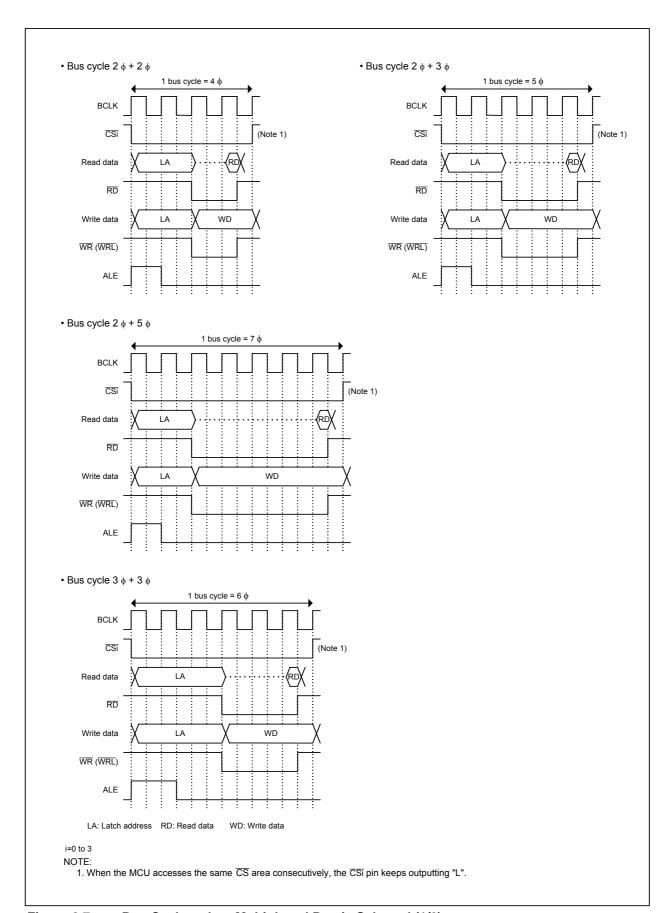

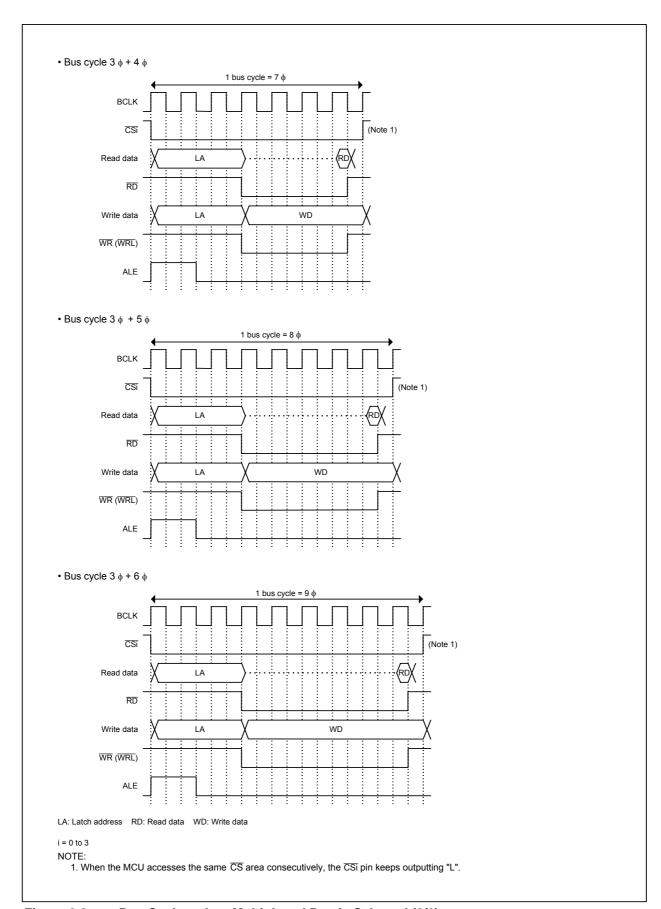

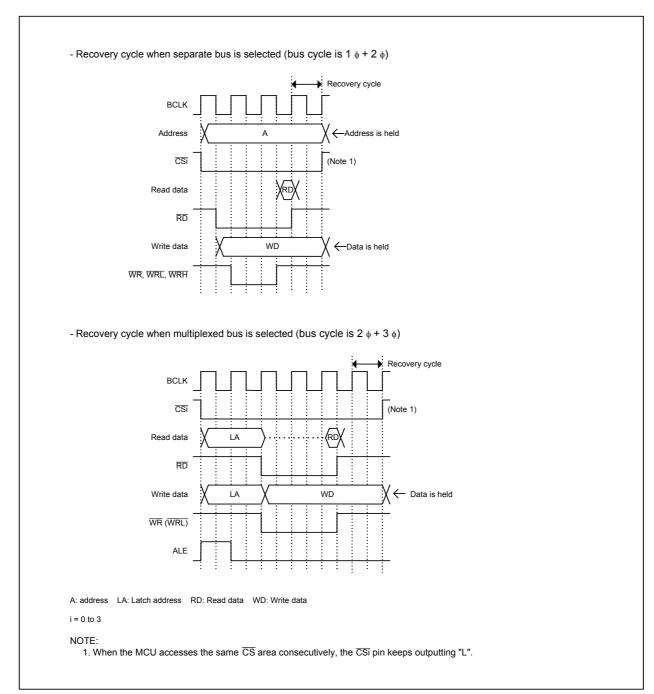

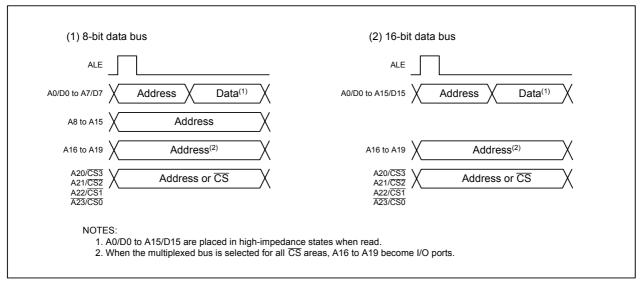

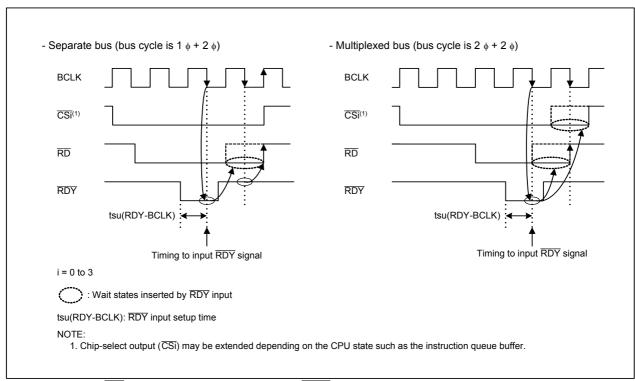

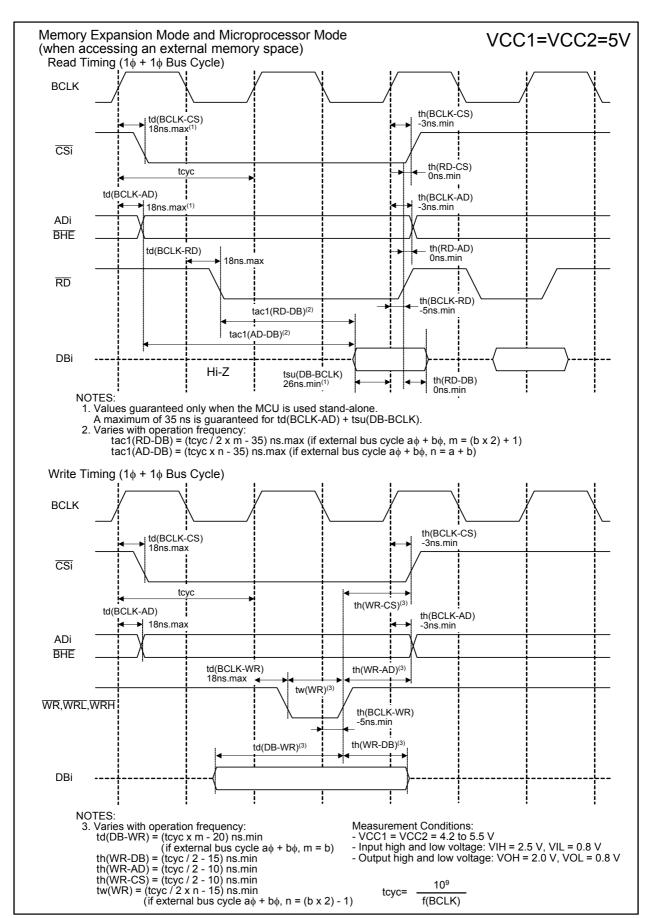

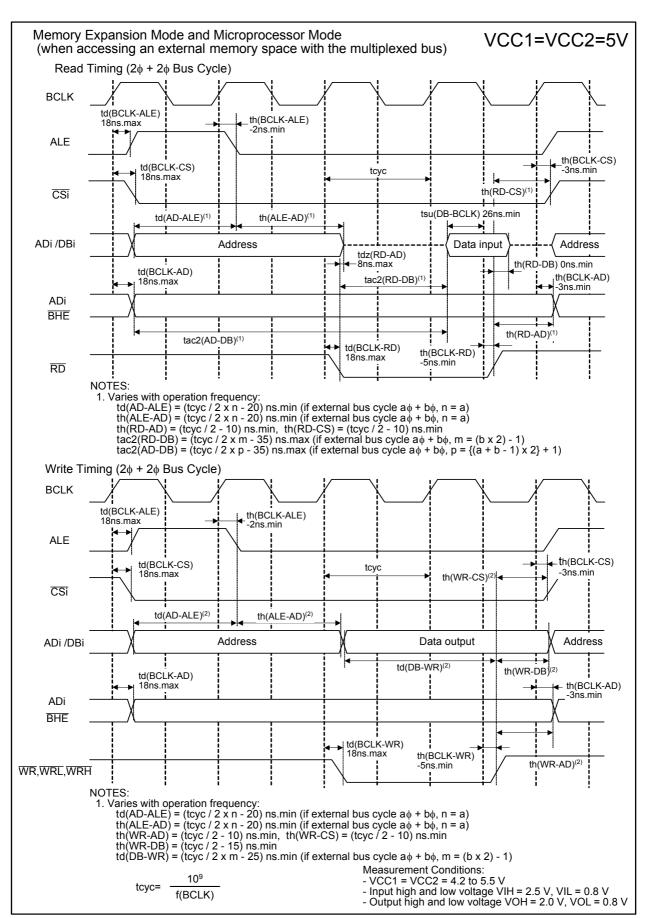

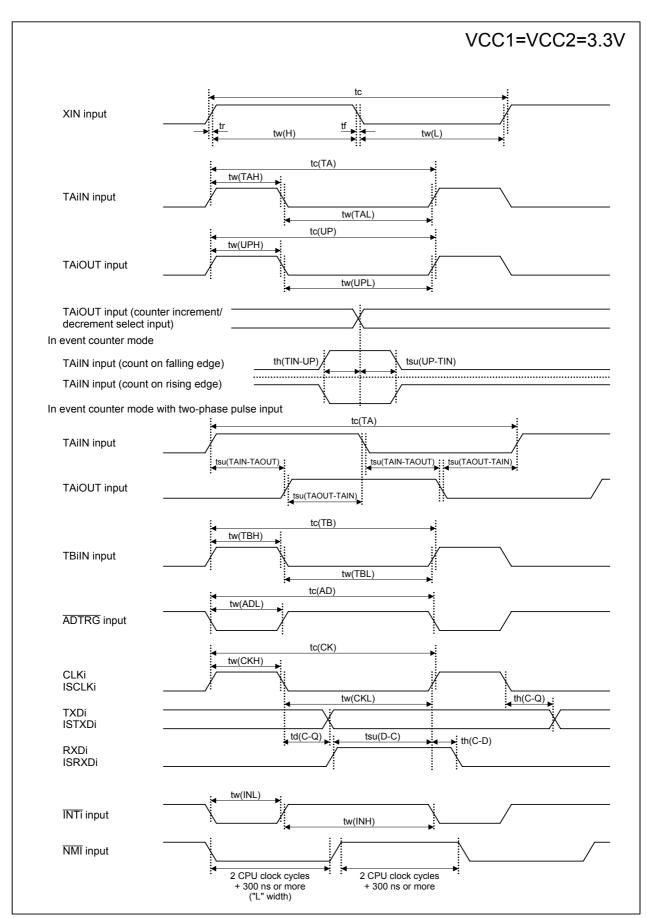

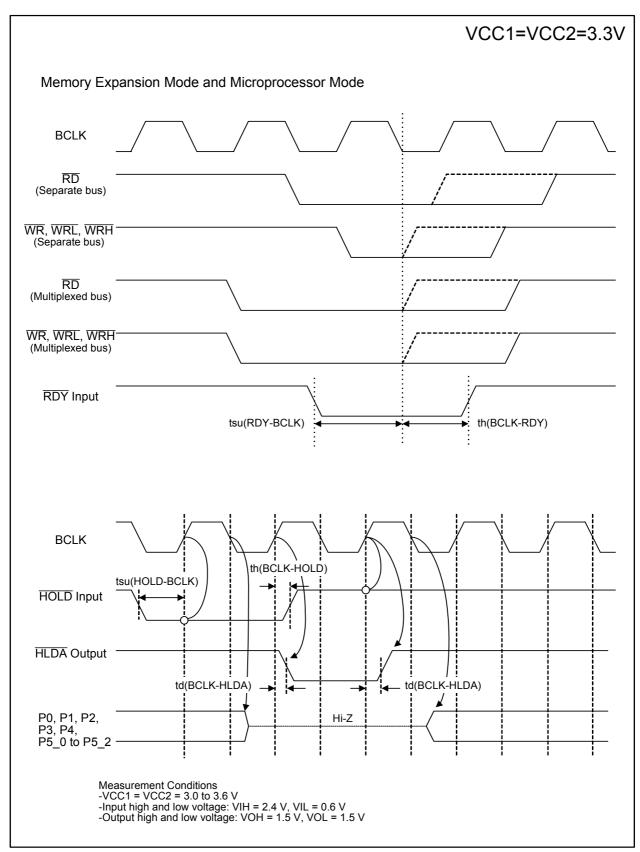

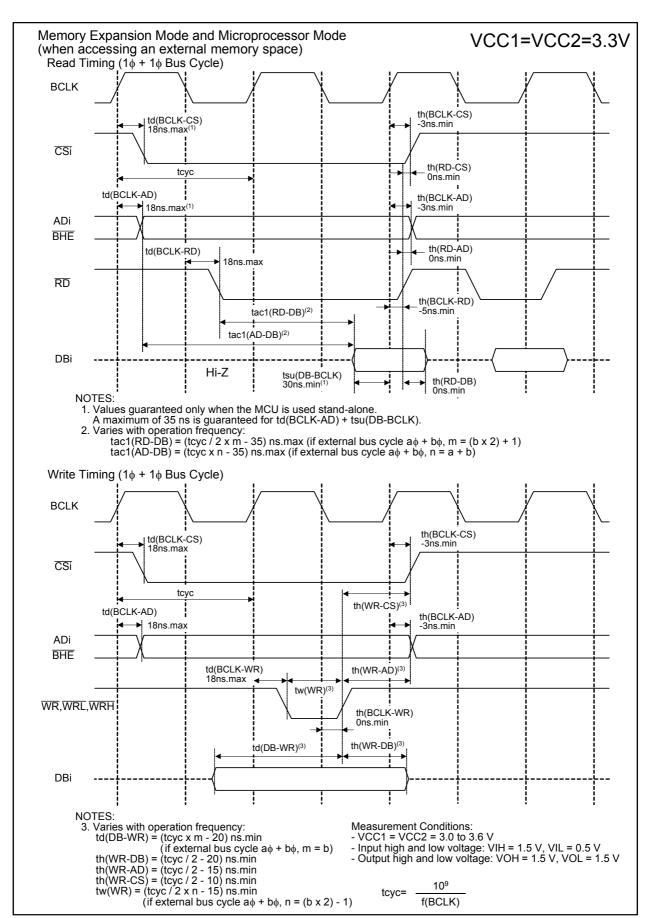

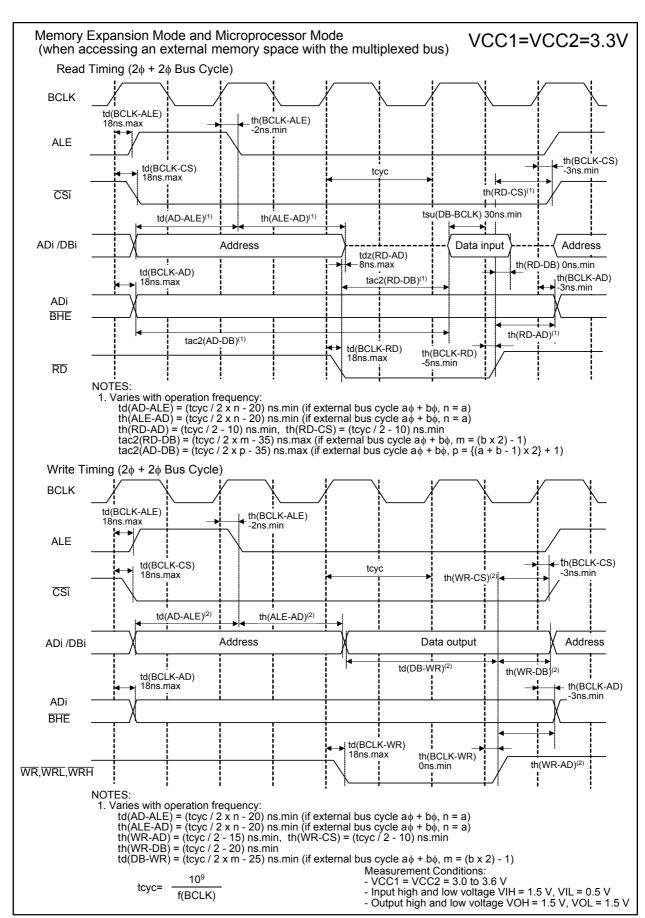

| 8.2.4        | Bus Timing                                             | 69  |

| 8.2.5        | ALE Output                                             |     |

| 8.2.6        | RDY Input                                              | 77  |

| 8.2.7        | HOLD Input                                             |     |

| 8.2.8        | External Bus States when Accessing Internal Space      |     |

| 8.2.9        | BCLK Output                                            |     |

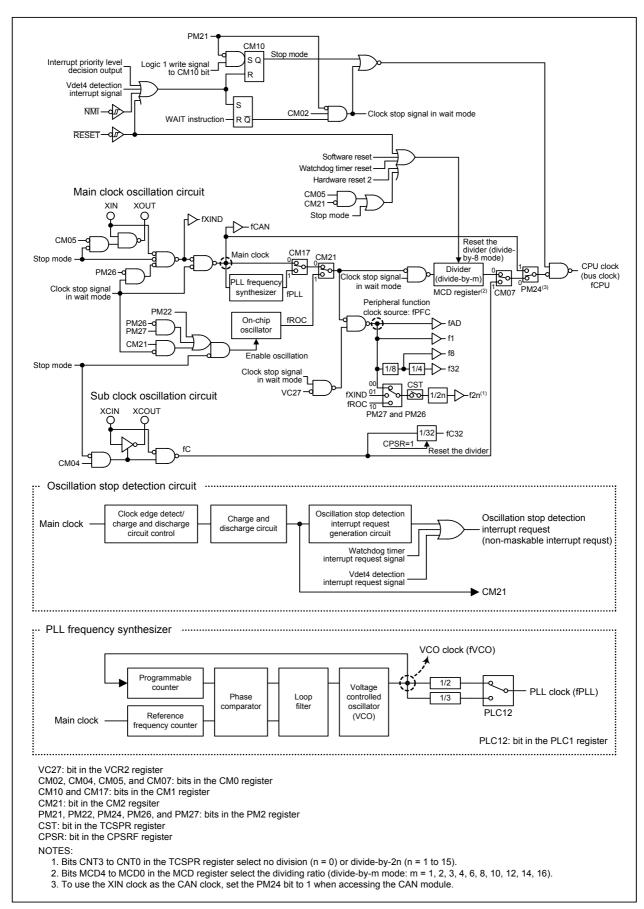

| 9. Clo       | ck Generation Circuits                                 | 80  |

| 9.1          | Types of the Clock Generation Circuit                  | 80  |

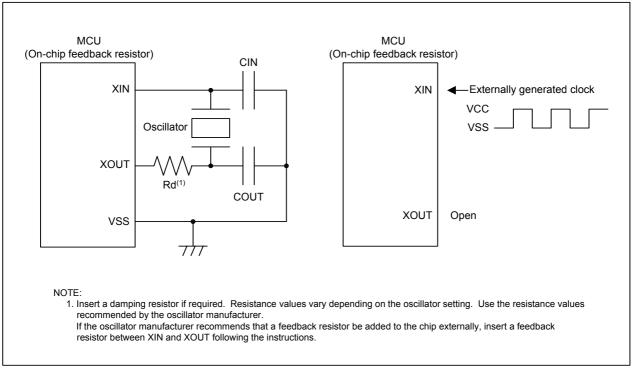

| 9.1.1        | Main Clock                                             | 89  |

| 9.1.2        | Sub Clock                                              | 90  |

| 9.1.3        | On-Chip Oscillator Clock                               | 91  |

| 9.1.4        | PLL Clock                                              | 93  |

| 9.2          | CPU Clock and BCLK                                     |     |

| 9.3          | Peripheral Function Clock                              |     |

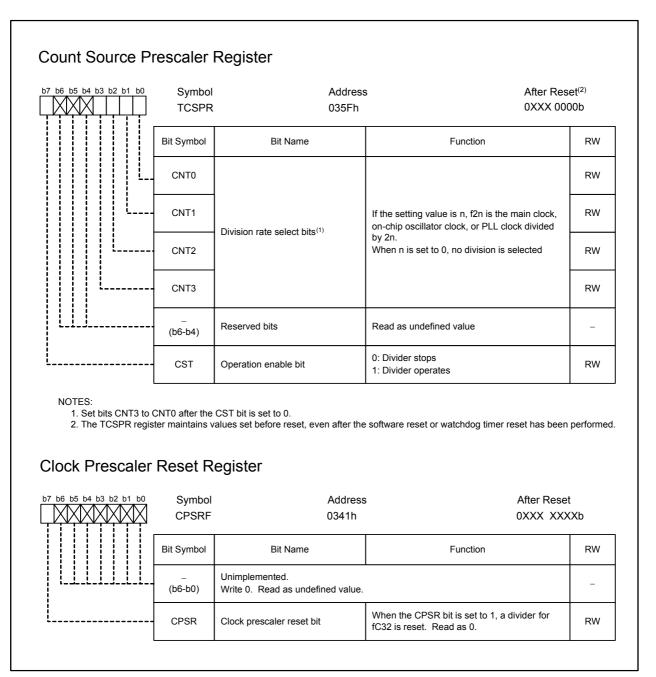

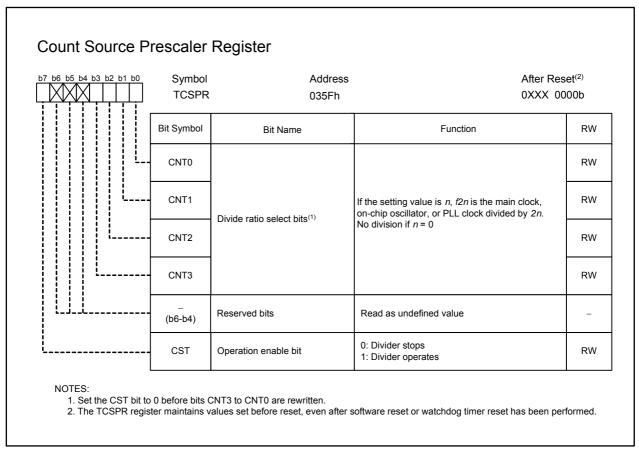

| 9.3.1        | f1, f8, f32, and f2n                                   |     |

| 9.3.2        | fAD                                                    | 94  |

| 9.3.3        | fC32                                                   | 94  |

| 9.3.4        | fCAN                                                   | 94  |

| 9.4          | Clock Output Function                                  |     |

| 9.5          | Power Consumption Control                              | 96  |

| 9.5.1        | CPU operating mode                                     |     |

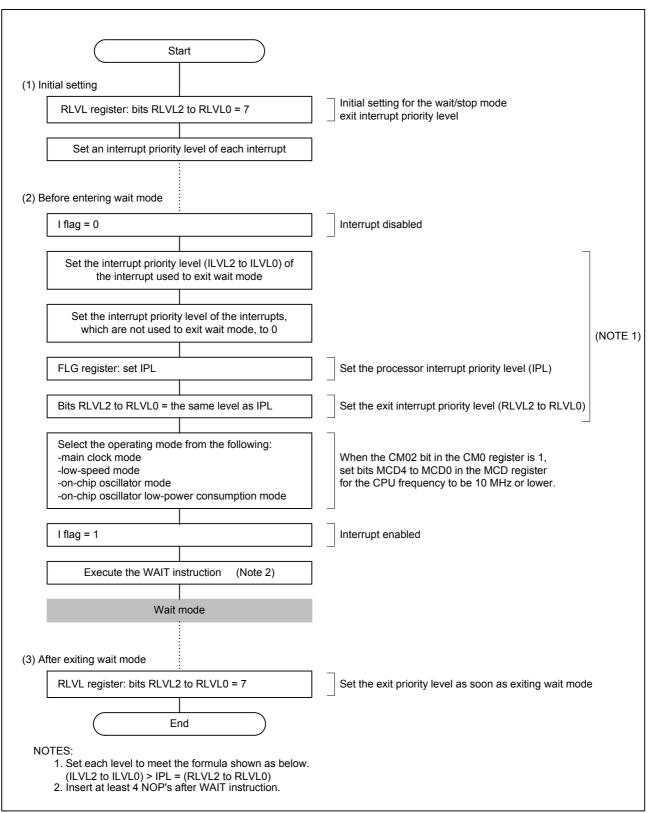

| 9.5.2        | Wait Mode                                              |     |

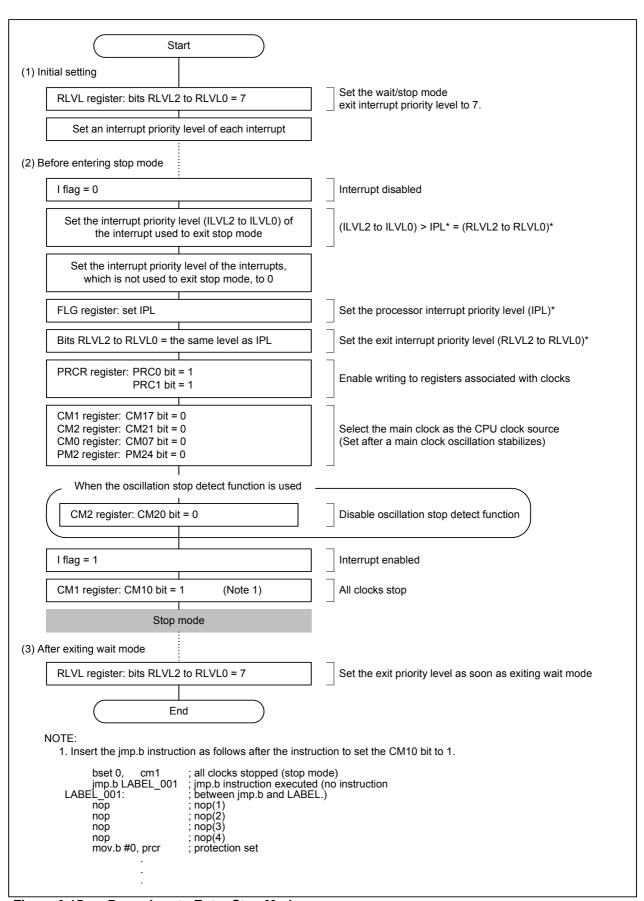

| 9.5.3        | Stop Mode                                              | 101 |

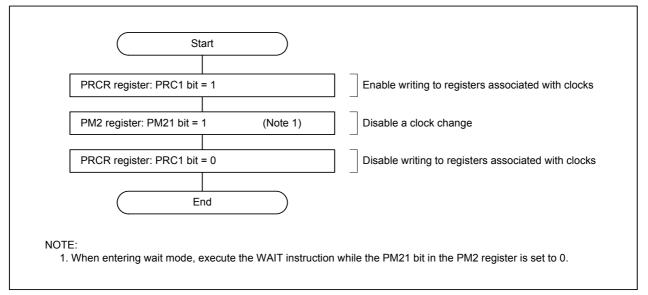

| 9.6          | System Clock Protect Function                          |     |

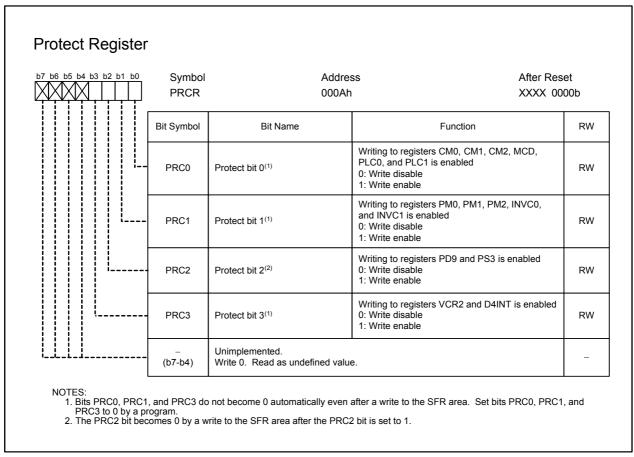

| 10. Pro      | tection                                                | 105 |

|              |                                                        |     |

|              | errupts                                                |     |

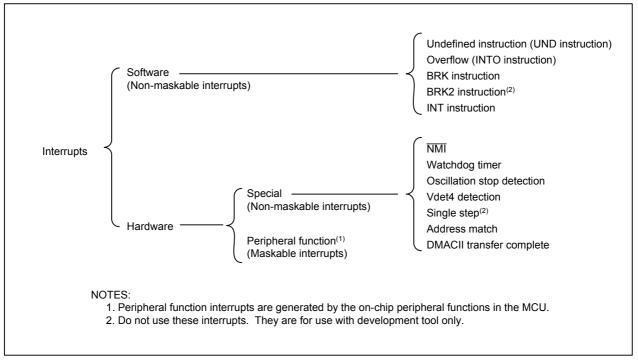

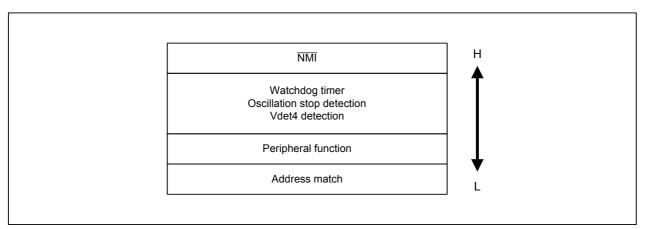

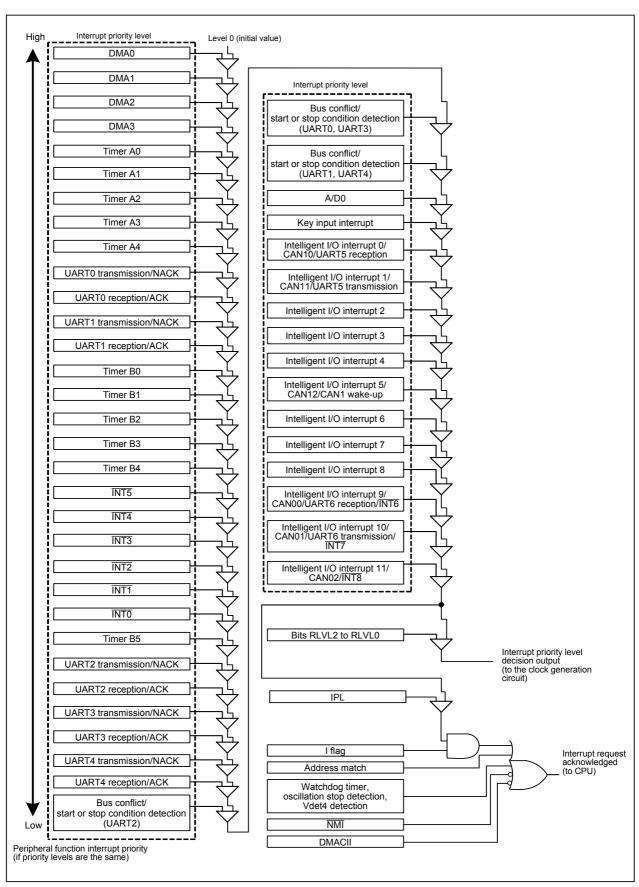

| 11.1         | Types of Interrupts                                    |     |

| 11.2         | Software Interrupts                                    |     |

| 11.2.1       | Undefined Instruction Interrupt                        |     |

| 11.2.2       | Overflow Interrupt                                     |     |

| 11.2.3       | BRK Interrupt                                          |     |

| 11.2.4       | BRK2 Interrupt                                         |     |

| 11.2.5       | INT Instruction Interrupt                              |     |

| 11.3         | Hardware Interrupts                                    |     |

| 11.3.1       | Special Interrupts                                     |     |

| 11.3.2       | DMACII End-of-Transfer Complete Interrupt              |     |

| 11.3.3       | Peripheral Function Interrupt                          |     |

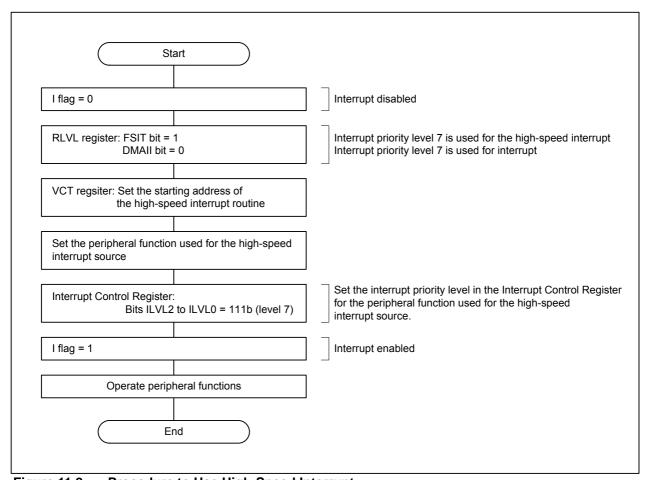

| 11.4<br>11.5 | High-Speed Interrupt  Interrupts and Interrupt Vectors |     |

|              | Fixed Vector Table                                     |     |

|              |                                                        |     |

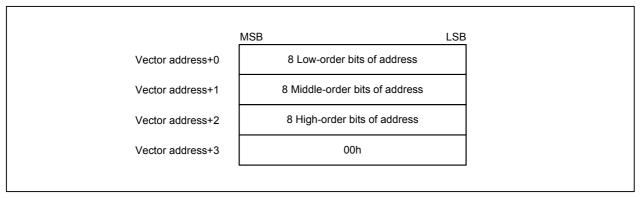

| 11.5.2 Relocatable Vector Table                                                                                            | 110 |

|----------------------------------------------------------------------------------------------------------------------------|-----|

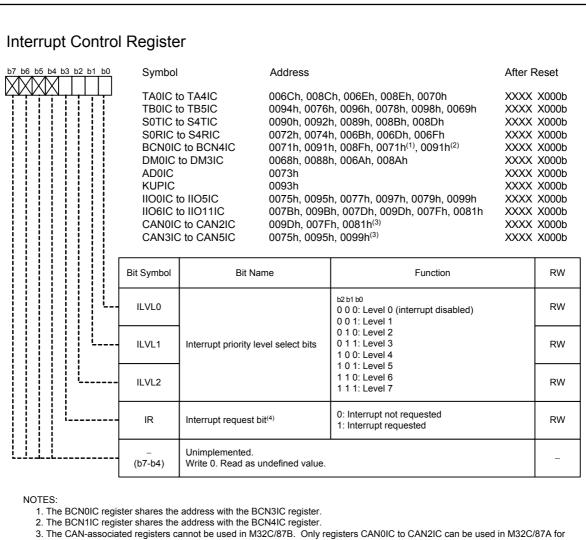

| 11.6 Interrupt Request Acknowledgement                                                                                     | 113 |

| 11.6.1 I Flag and IPL                                                                                                      | 113 |

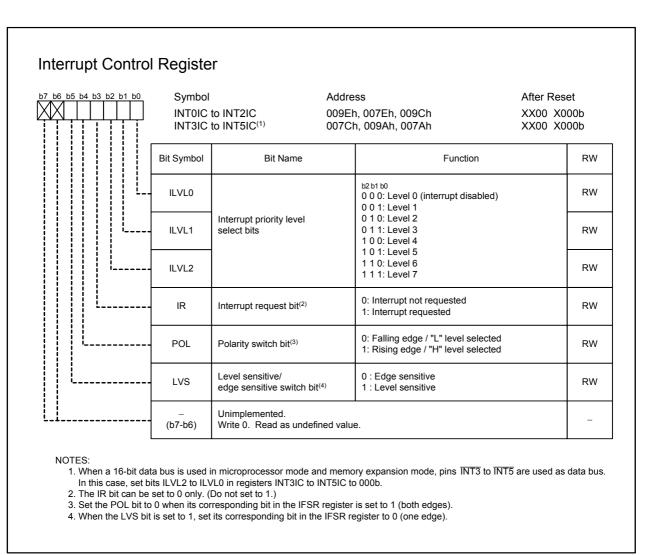

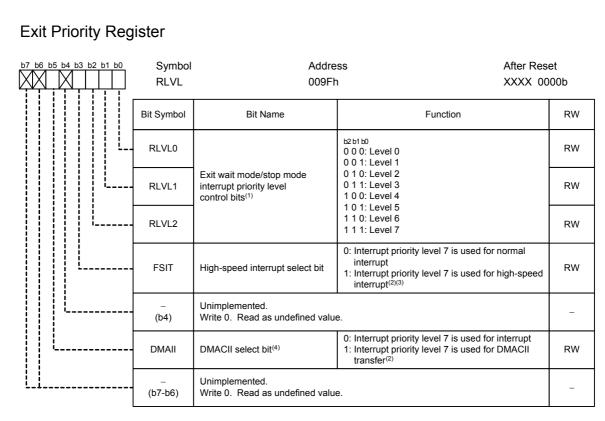

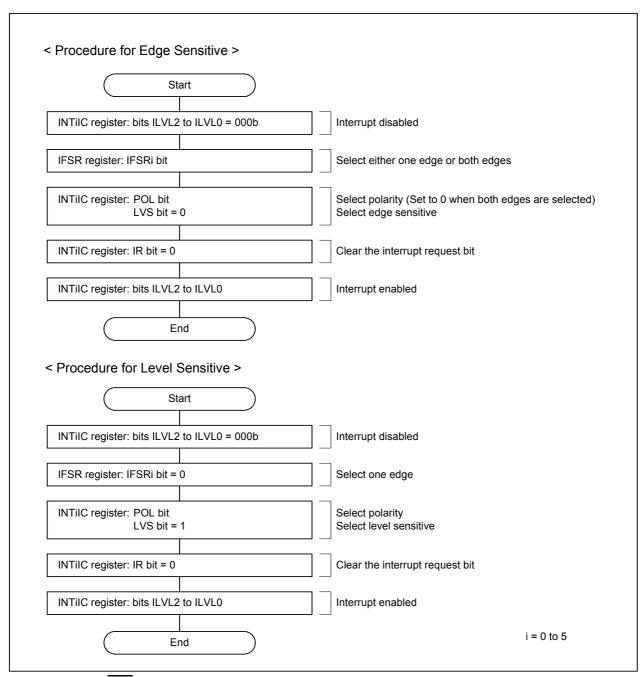

| 11.6.2 Interrupt Control Registers and RLVL Register                                                                       | 113 |

| 11.6.3 Interrupt Sequence                                                                                                  | 117 |

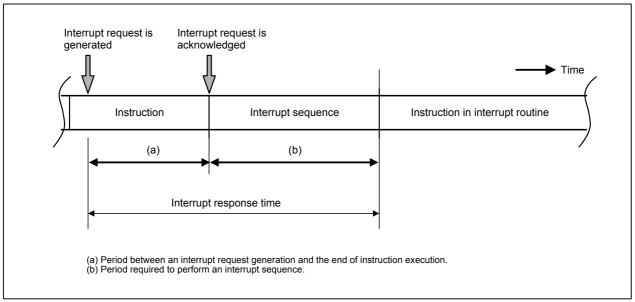

| 11.6.4 Interrupt Response Time                                                                                             | 118 |

| 11.6.5 IPL Change when Interrupt Request is Acknowledged                                                                   |     |

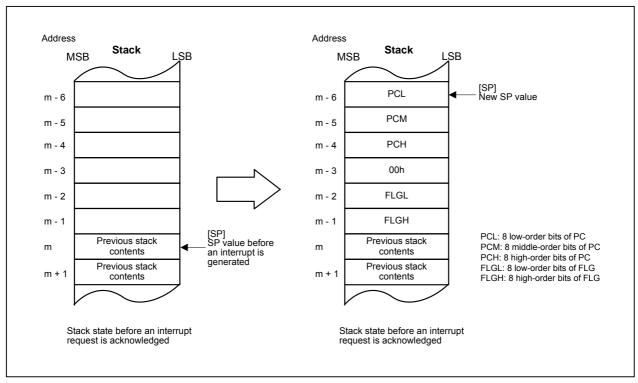

| 11.6.6 Saving a Register                                                                                                   | 119 |

| 11.6.7 Returning from Interrupt Routine                                                                                    | 120 |

| 11.6.8 Interrupt Priority                                                                                                  | 120 |

| 11.6.9 Interrupt Priority Level Decision Circuit                                                                           | 120 |

| 11.7 Interrupt                                                                                                             |     |

| 11.8 NMI Interrupt                                                                                                         |     |

| 11.9 Key Input Interrupt                                                                                                   |     |

| 11.10 Address Match Interrupt                                                                                              | 127 |

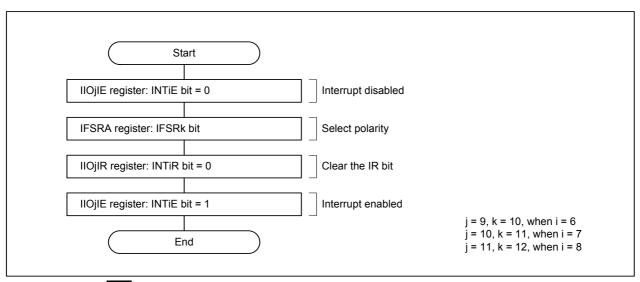

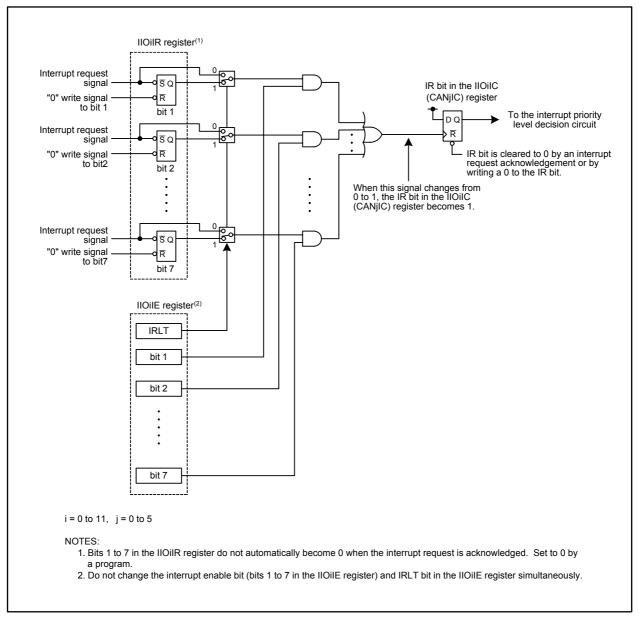

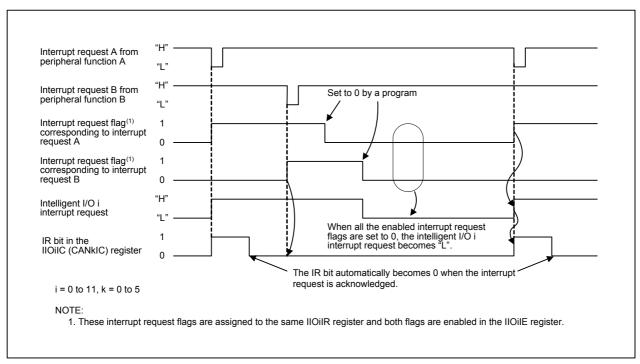

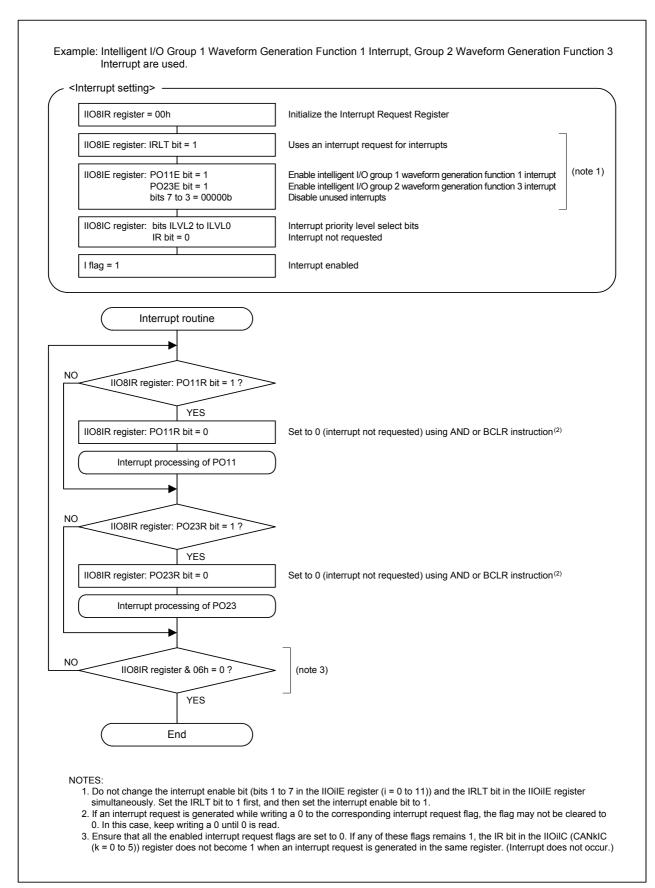

| 11.11 Intelligent I/O Interrupts, CAN Interrupts, UART5 and UART6 Transmit/Receive Interrupts, and INT6 to INT8 Interrupts | 128 |

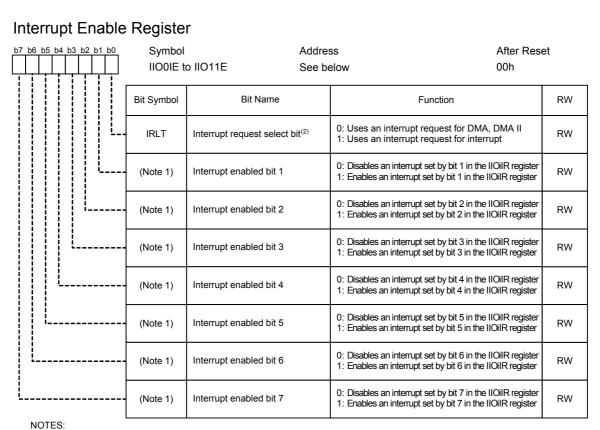

| 11.11.1 IIOiIE Register                                                                                                    | 131 |

| 11.11.2 IIOiIR Register                                                                                                    | 131 |

| 11.11.3 IIOiIC (CANjIC) Register                                                                                           | 131 |

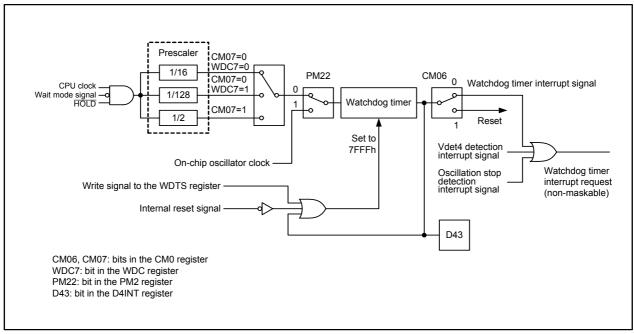

| 12. Watchdog Timer                                                                                                         |     |

| 13.1 Transfer Cycles                                                                                                       |     |

| 13.1.1 Effect of Source and Destination Addresses                                                                          |     |

| 13.1.2 Effect of bodiec and Destination Addresses                                                                          |     |

| 13.1.3 Effect of Software Wait State                                                                                       |     |

| 13.1.4 Effect of the RDY Signal                                                                                            |     |

| 13.2 DMA Transfer Time                                                                                                     |     |

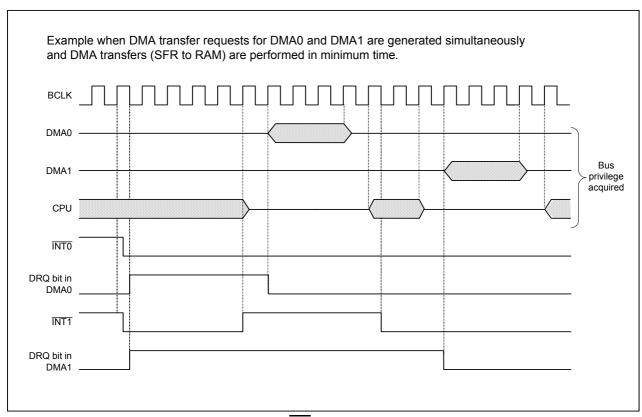

| 13.3 Channel Priority and DMA Transfer Timing                                                                              |     |

| 14 DMACII                                                                                                                  | 151 |

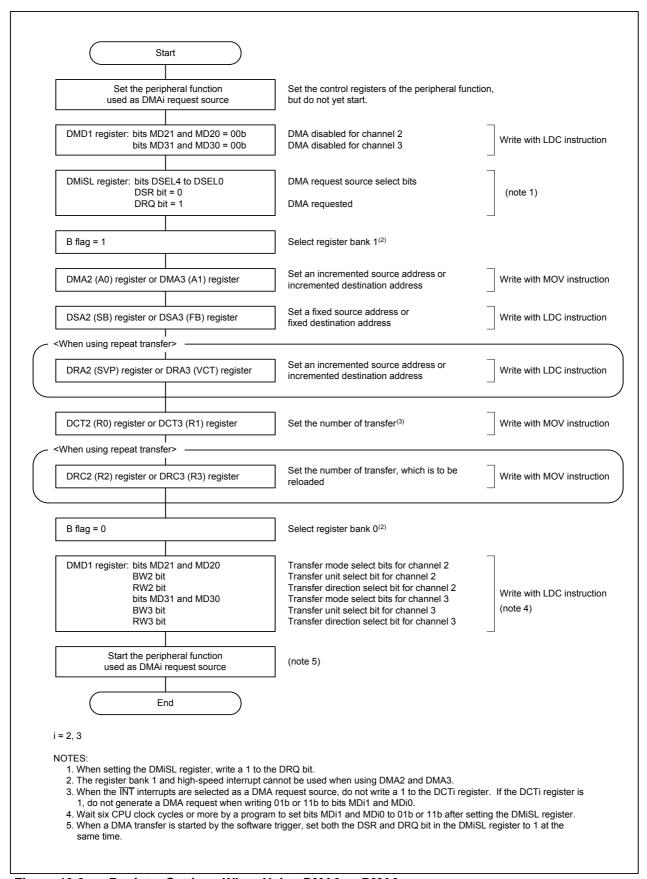

| 14.1 DMACII Settings                                                                                                       |     |

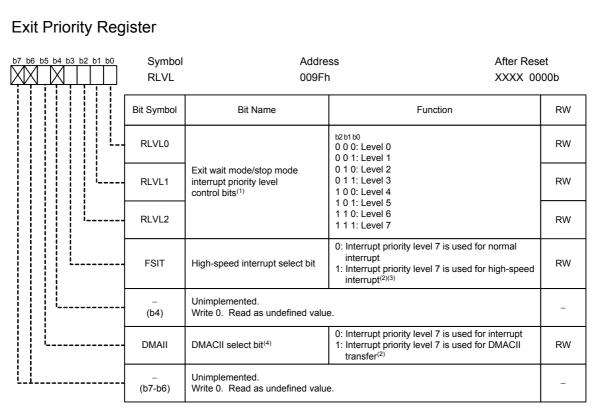

| 14.1.1 RLVL Register                                                                                                       |     |

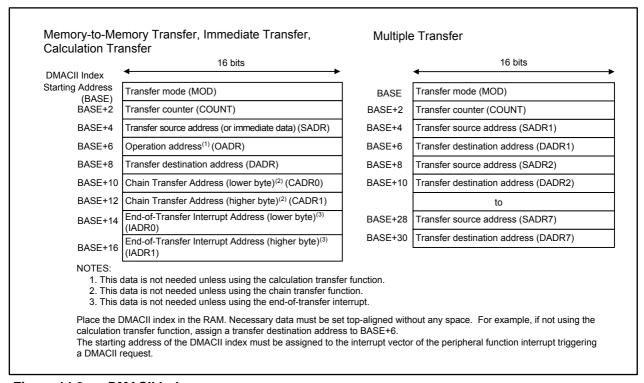

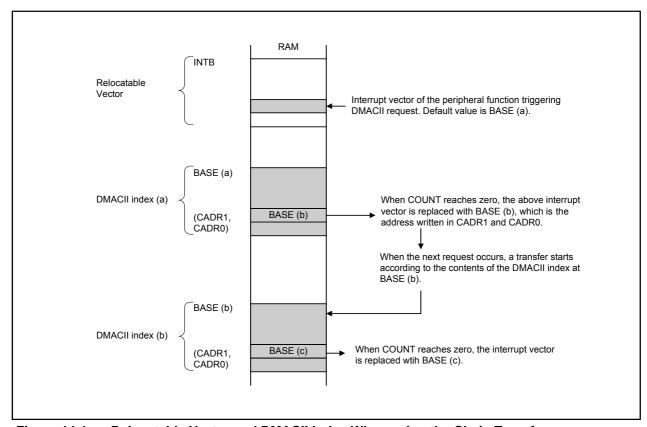

| 14.1.2 DMACII Index                                                                                                        |     |

| 14.1.3 Interrupt Control Register for the Peripheral Function                                                              |     |

| 14.1.4 Relocatable Vector Table for the Peripheral Function                                                                |     |

| 14.1.5 IRLT Bit in the IIOiIE Register (i = 0 to 11)                                                                       |     |

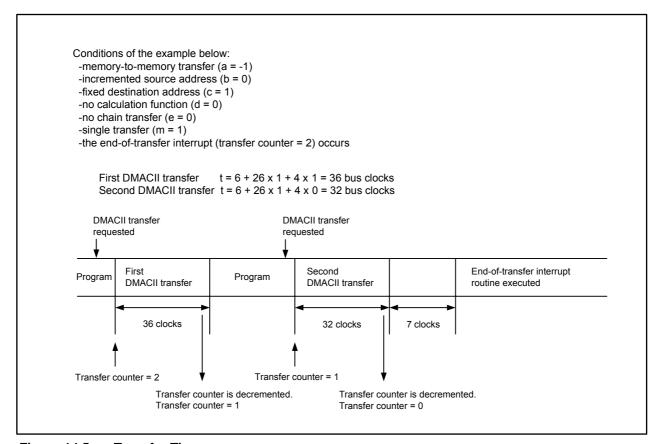

| 14.2 DMACII Performance                                                                                                    |     |

| 14.3 Transfer Data                                                                                                         |     |

| 14.3.1 Memory-to-memory Transfer                                                                                           |     |

| 14.3.2 Immediate Data Transfer                                                                                             |     |

| 14.3.3 Calculation Transfer                                                                                                |     |

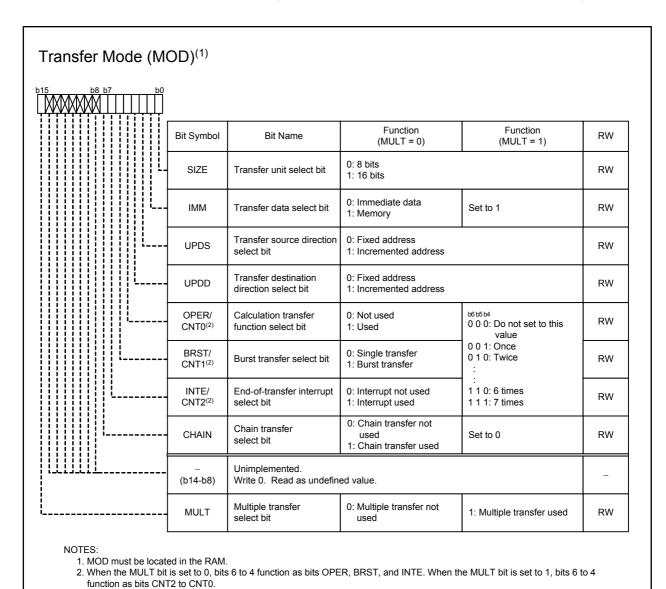

| 14.4 Transfer Modes                                                                                                        | 156 |

| 14.4.1 Single Transfer                                                                                                     | 156 |

| 14.4.2 Burst Transfer                                                                                                      | 156 |

| 14.4.3 Multiple Transfer                                                                                                   | 156 |

| 14.5 Chain Transfer                                                                                                        | 157 |

| 14.6 End-of-Transfer Interrupt                                                                                             | 157 |

| 14.7    | Execution Time                                                     | 158 |

|---------|--------------------------------------------------------------------|-----|

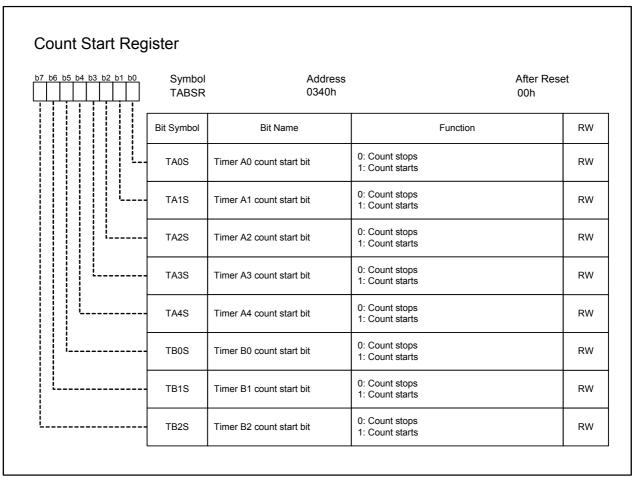

| 15. Tim | ners                                                               | 159 |

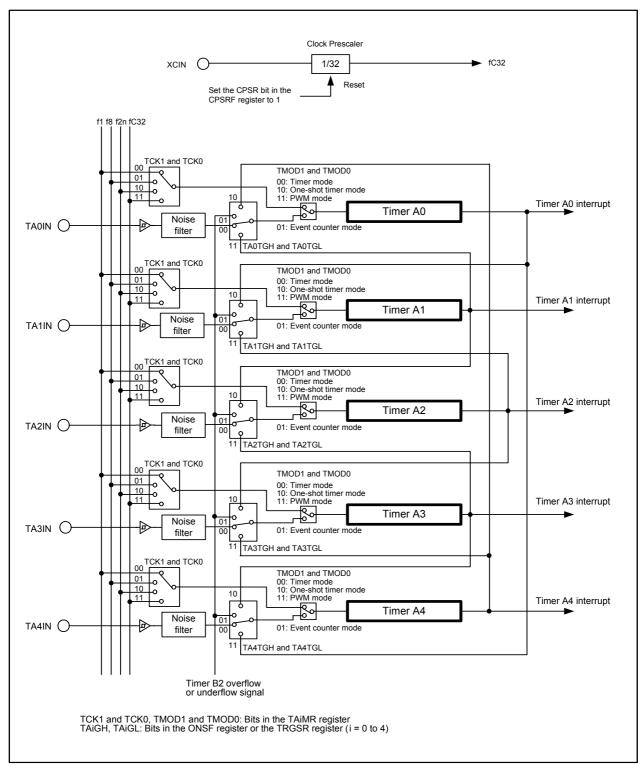

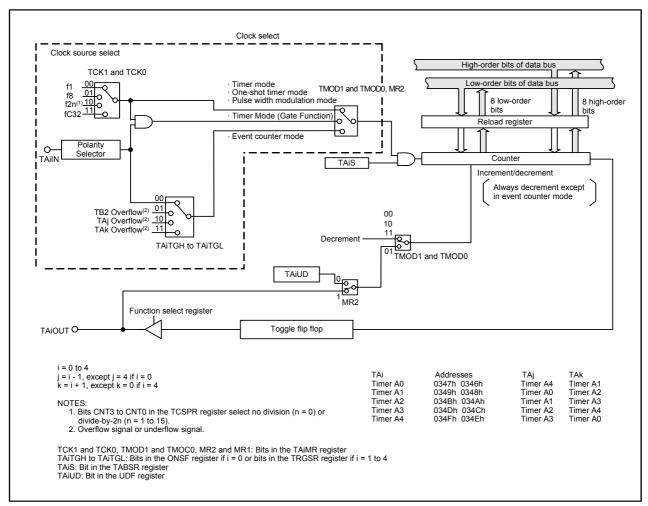

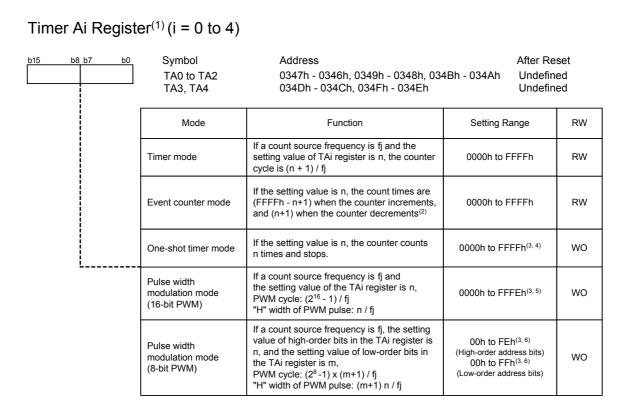

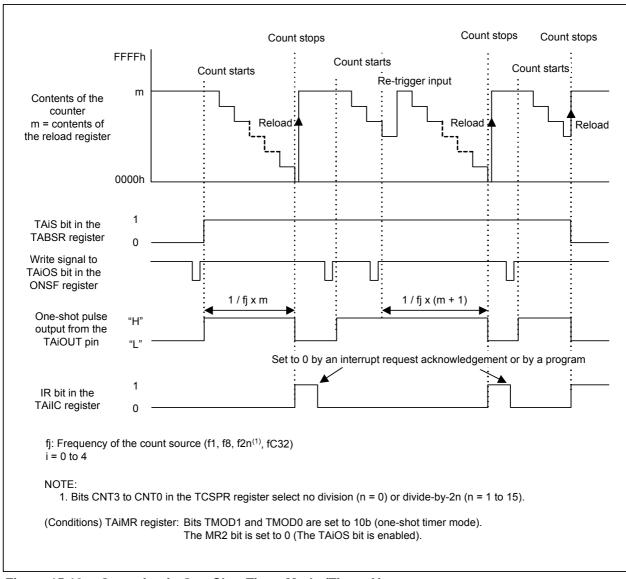

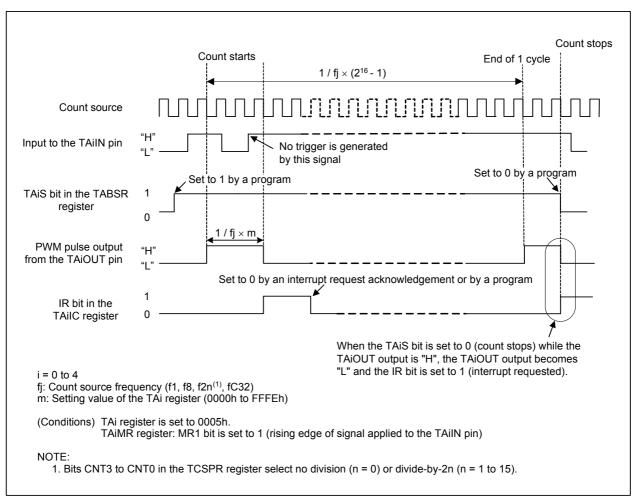

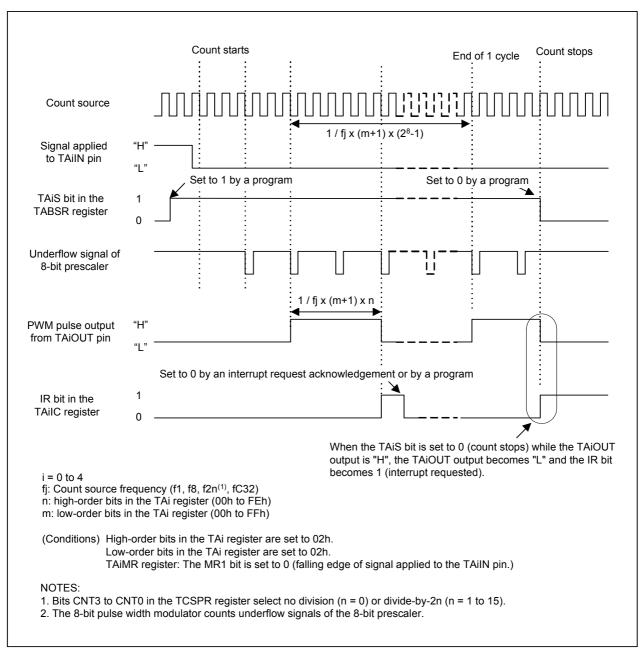

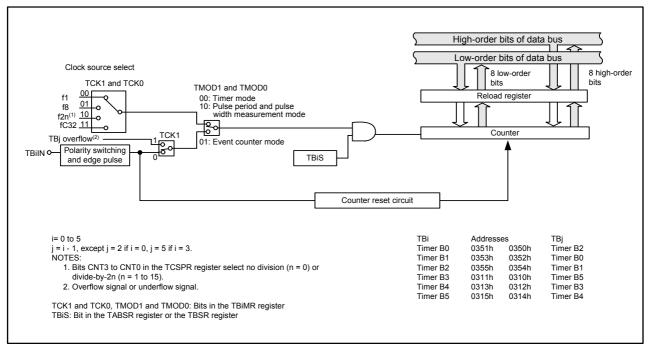

| 15.1    | Timer A                                                            | 161 |

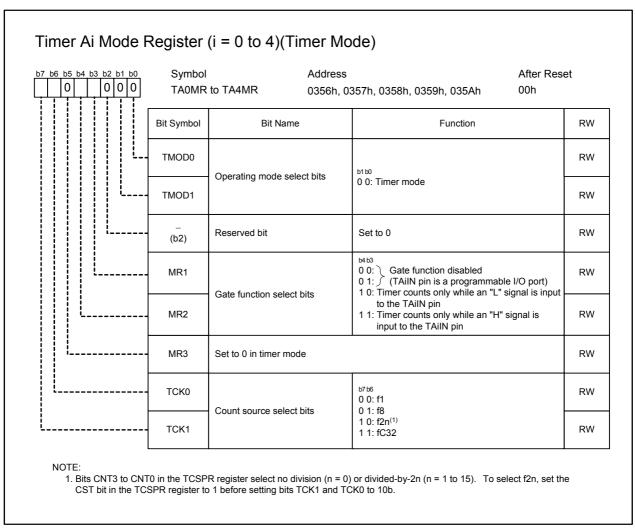

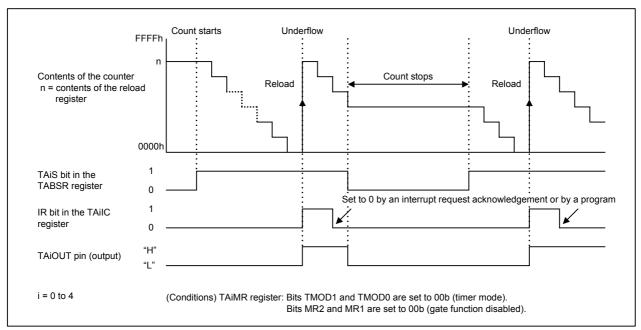

| 15.1.1  | Timer Mode                                                         | 173 |

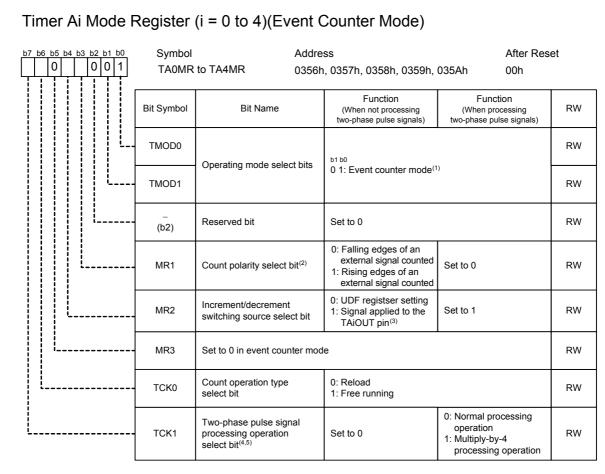

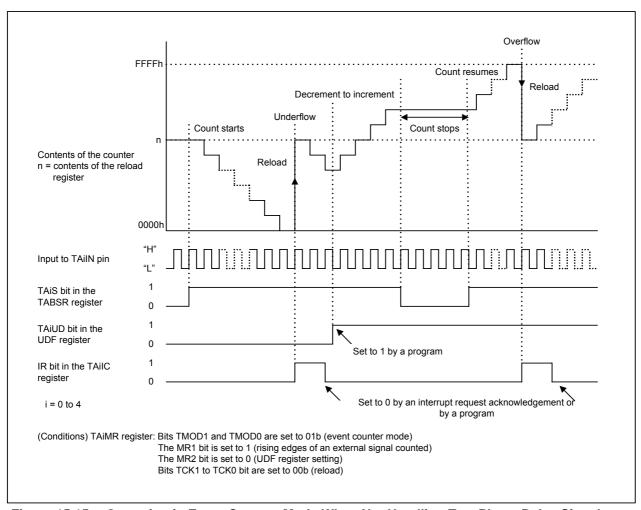

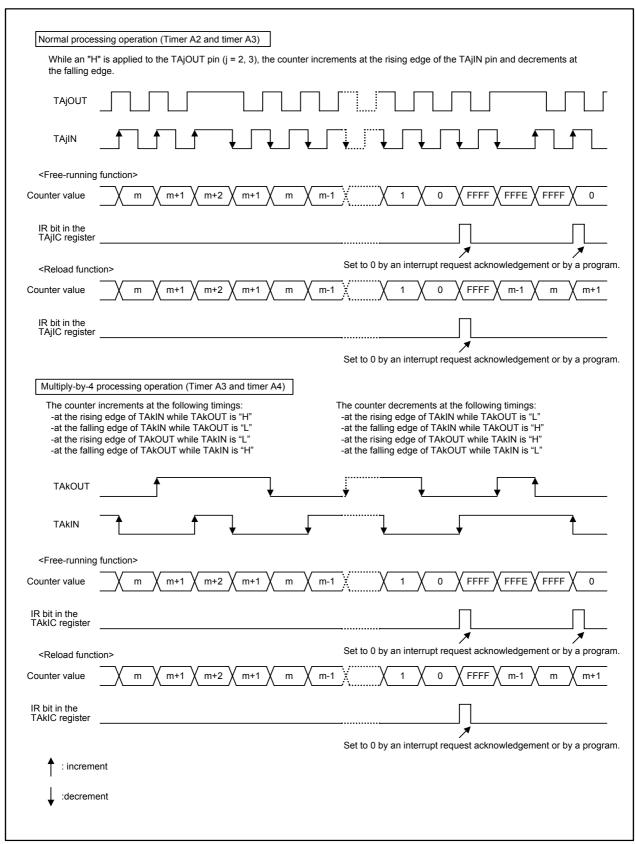

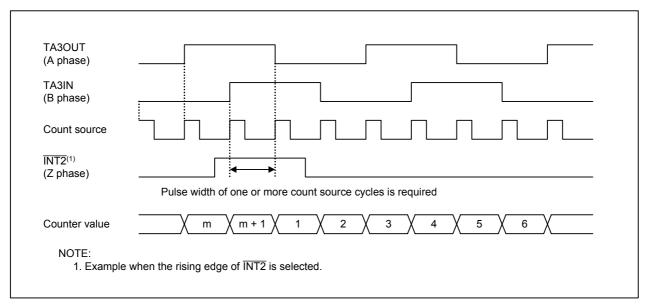

| 15.1.2  | Event Counter Mode                                                 | 174 |

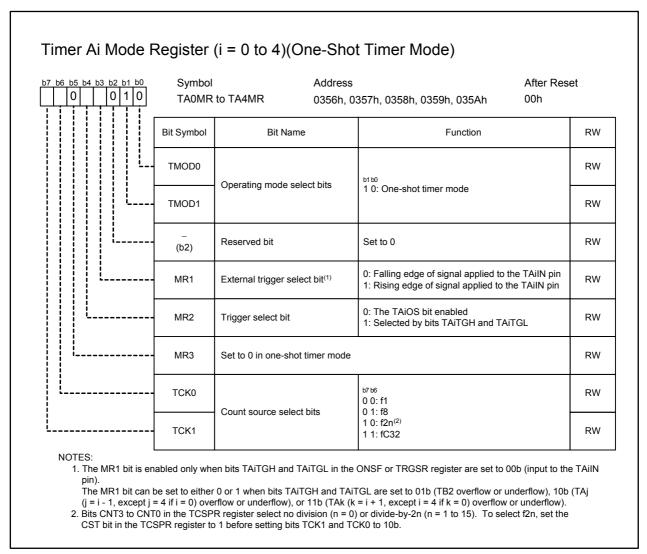

| 15.1.3  | One-Shot Timer Mode                                                | 179 |

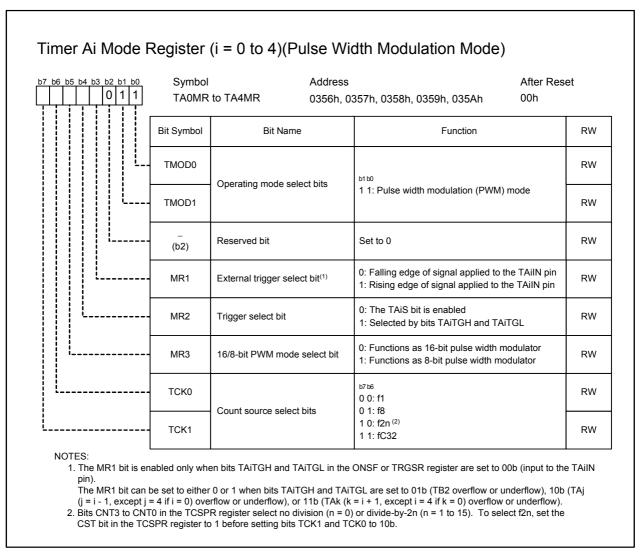

| 15.1.4  | Pulse Width Modulation Mode                                        | 181 |

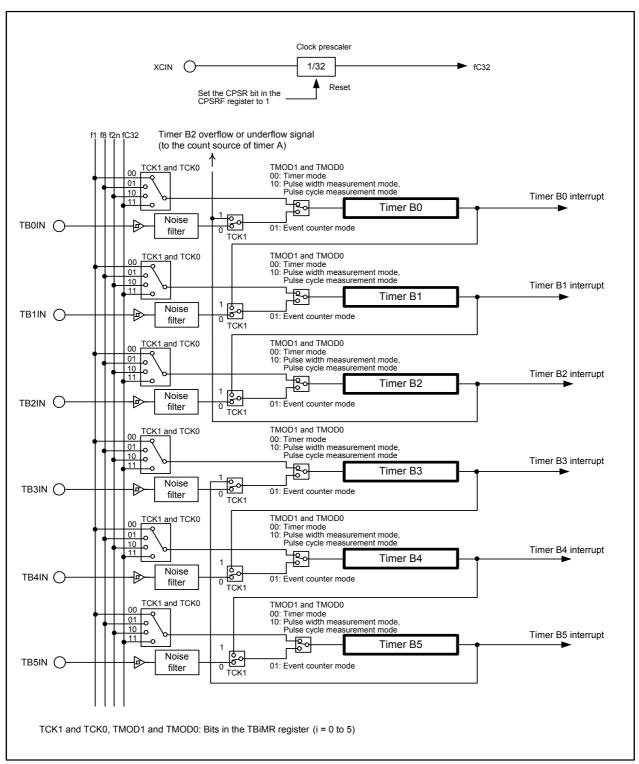

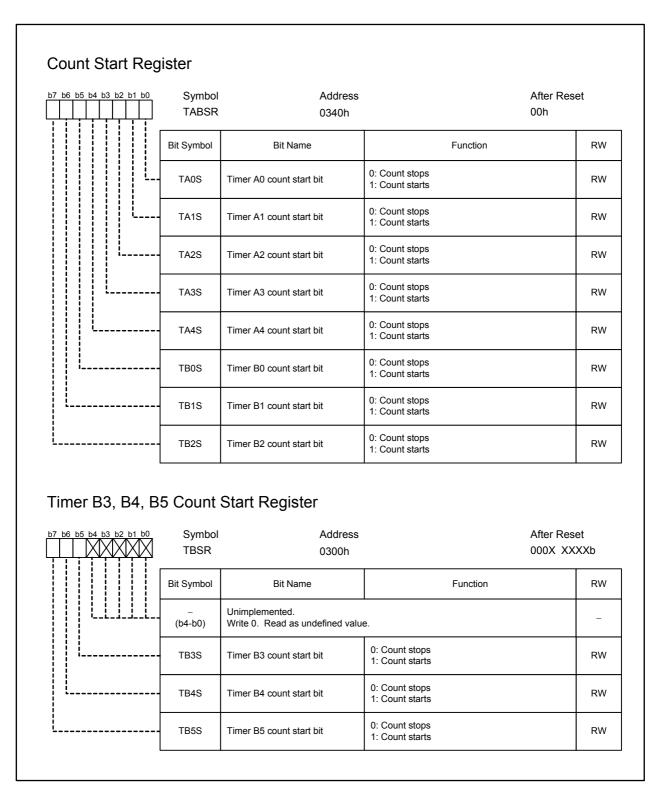

| 15.2    | Timer B                                                            | 184 |

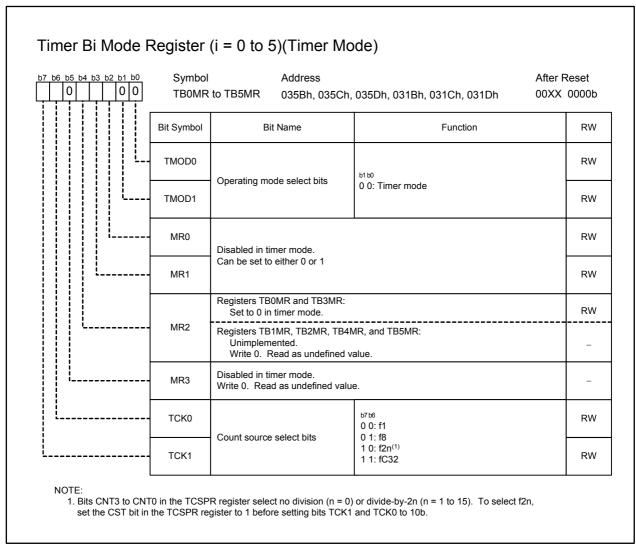

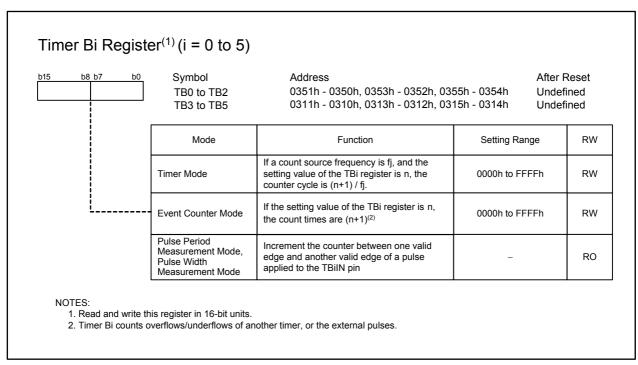

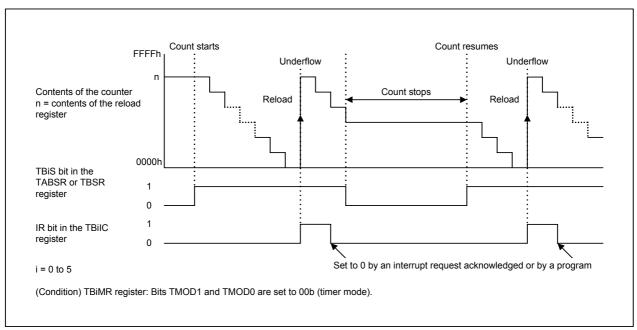

| 15.2.1  | Timer Mode                                                         | 191 |

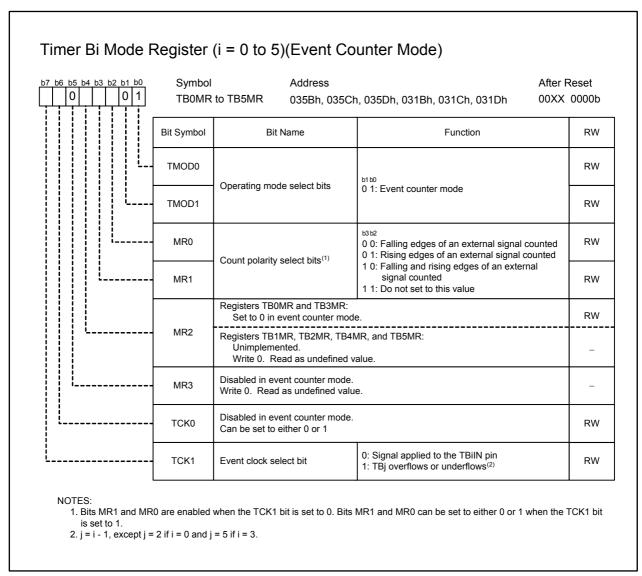

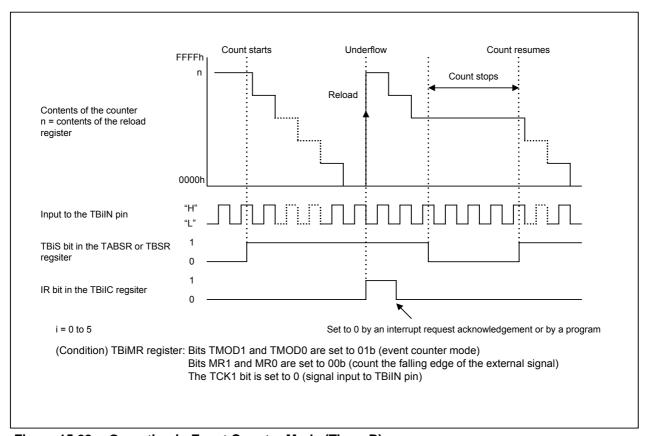

| 15.2.2  | Event Counter Mode                                                 | 192 |

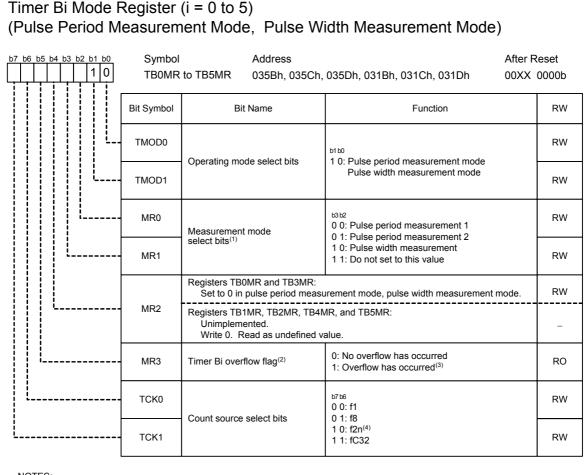

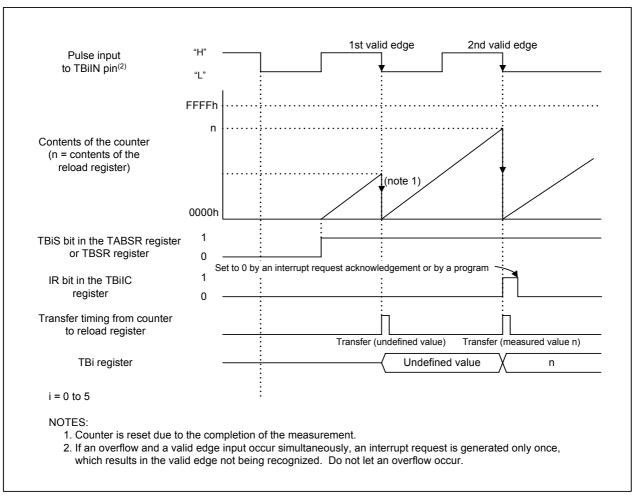

| 15.2.3  | Pulse Period Measurement Mode, Pulse Width Measurement Mode        | 193 |

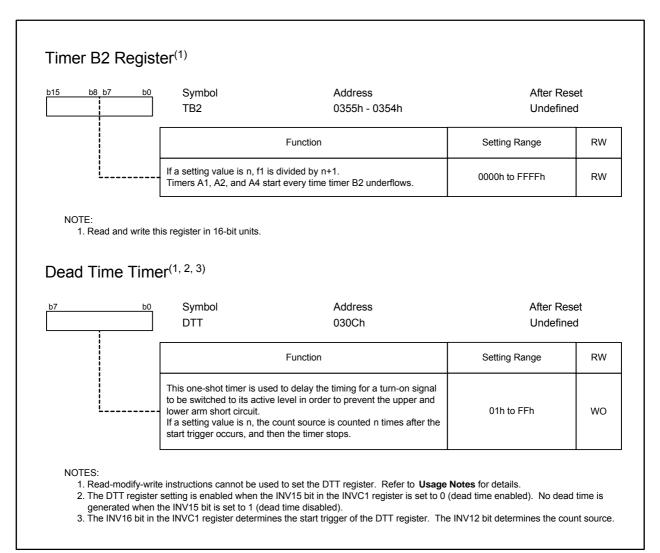

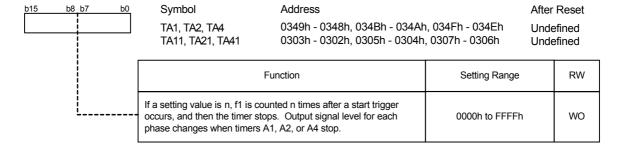

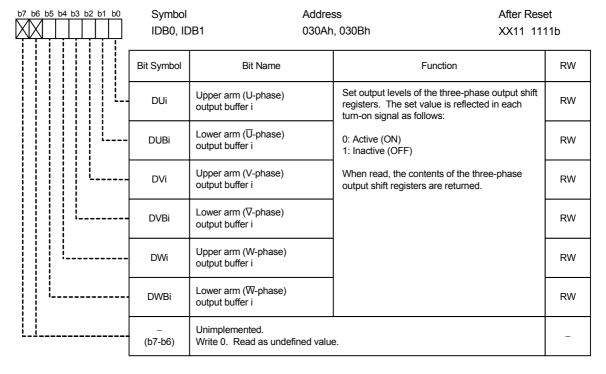

| 16. Thi | ree-Phase Motor Control Timer Function                             | 196 |

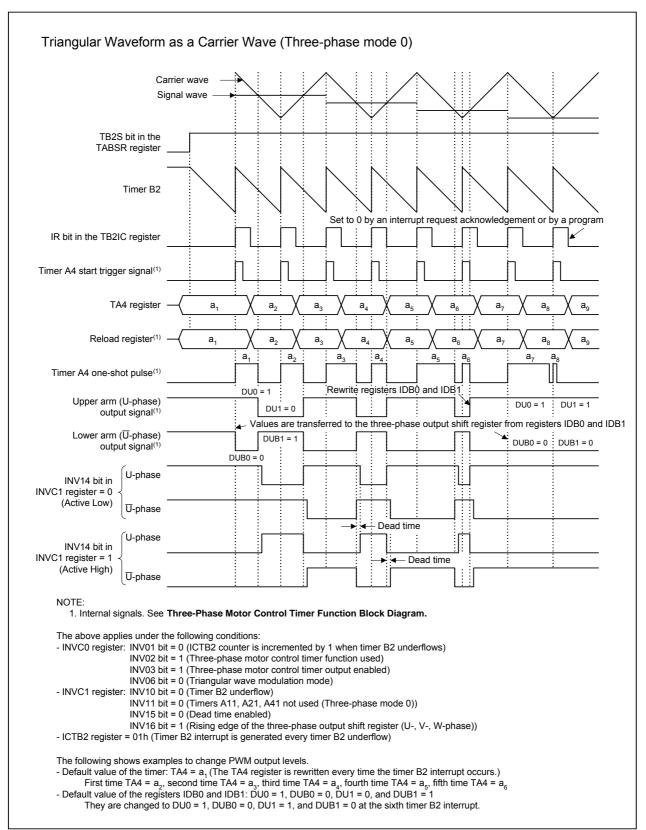

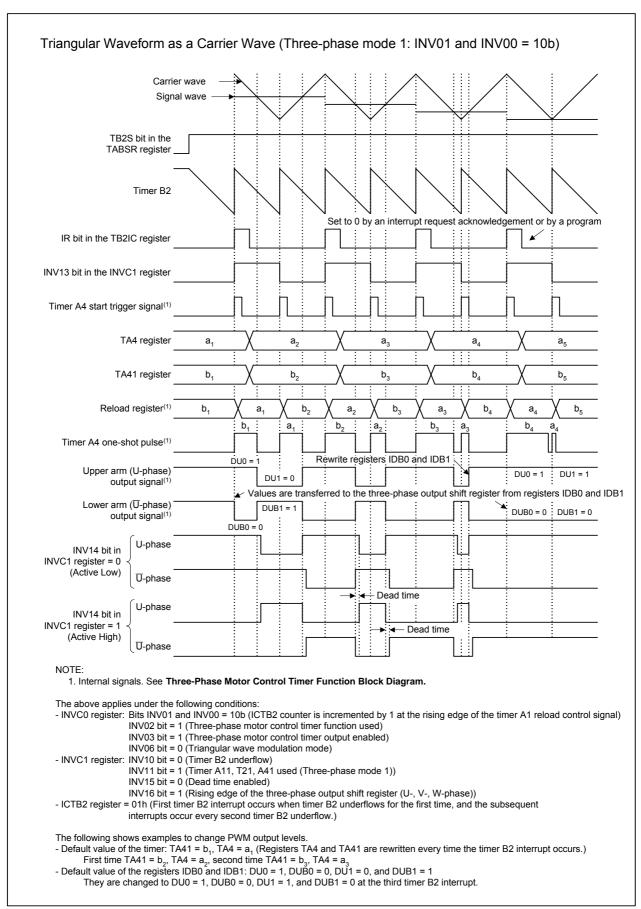

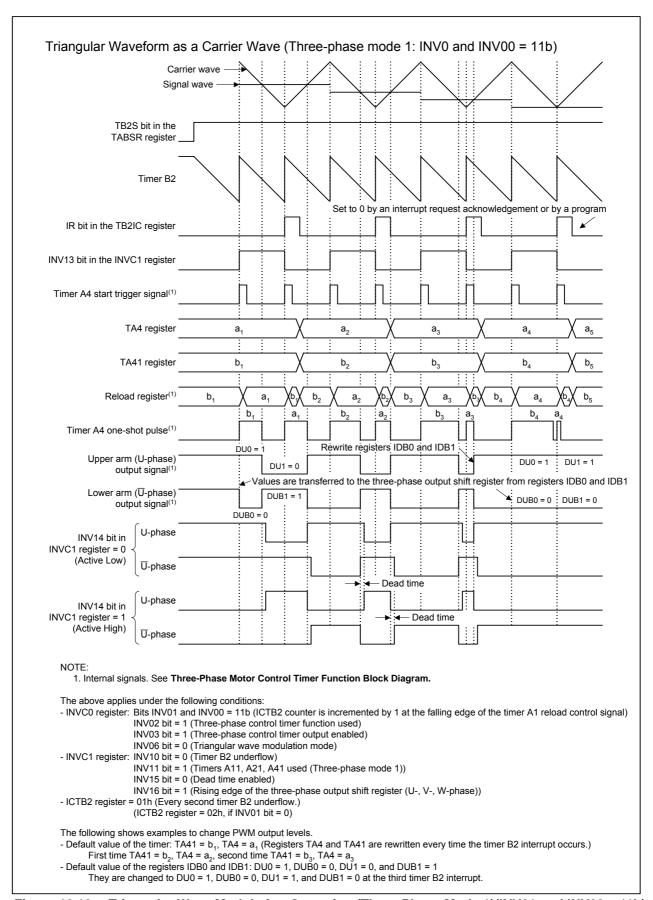

| 16.1    | Triangular Wave Modulation Mode                                    | 207 |

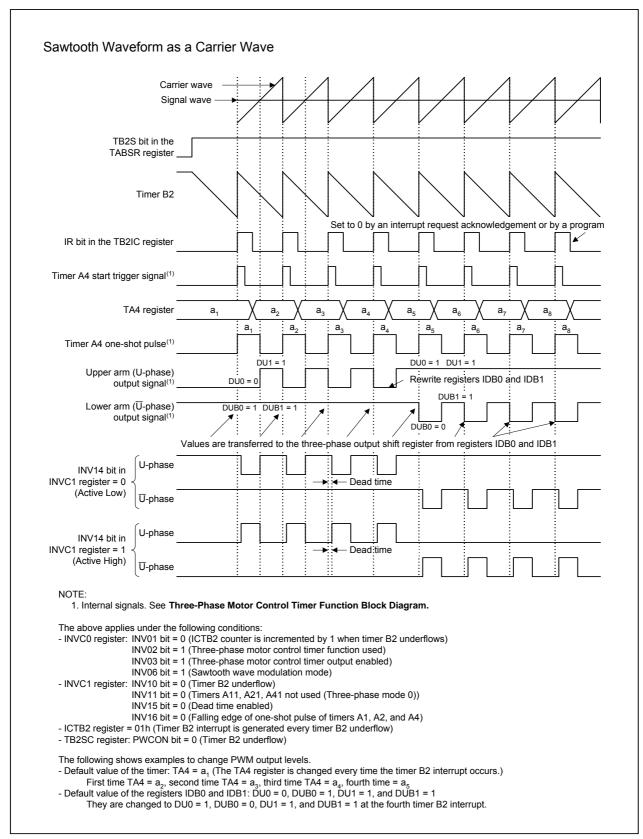

| 16.2    | Sawtooth Wave Modulation Mode                                      |     |

| 16.3    | Short Circuit Prevention Features                                  | 213 |

| 16.3.1  | Prevention Against Upper/Lower Arm Short Circuit by Program Errors | 213 |

| 16.3.2  | Arm Short Circuit Prevention Using Dead Time Timer                 | 213 |

| 16.3.3  | Forced-Cutoff Function by the NMI Input                            | 213 |

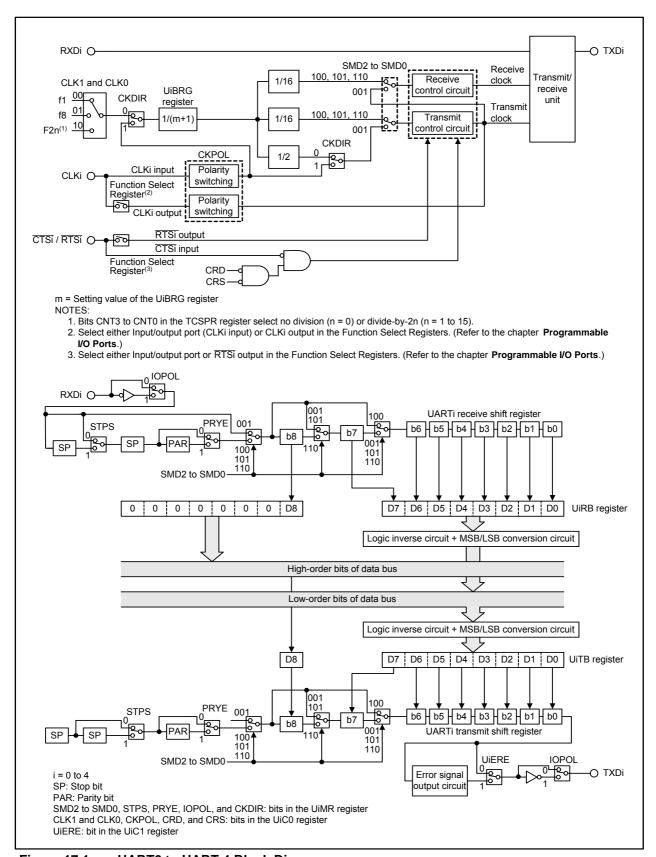

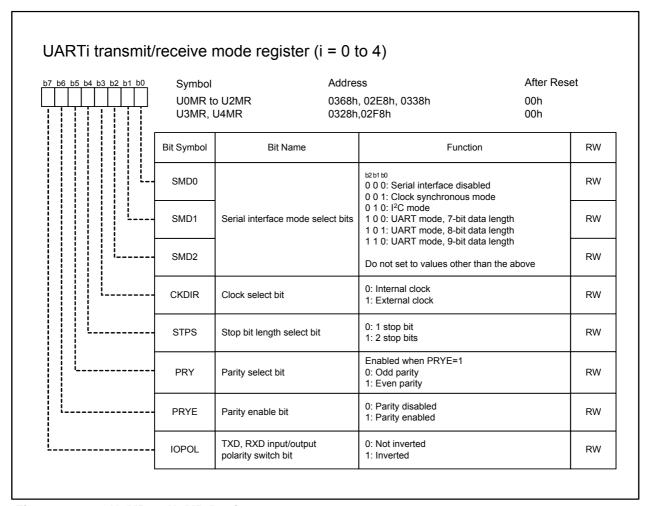

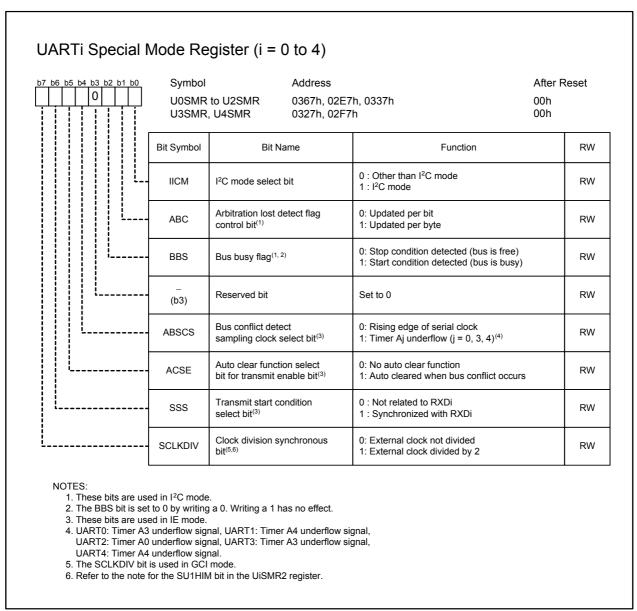

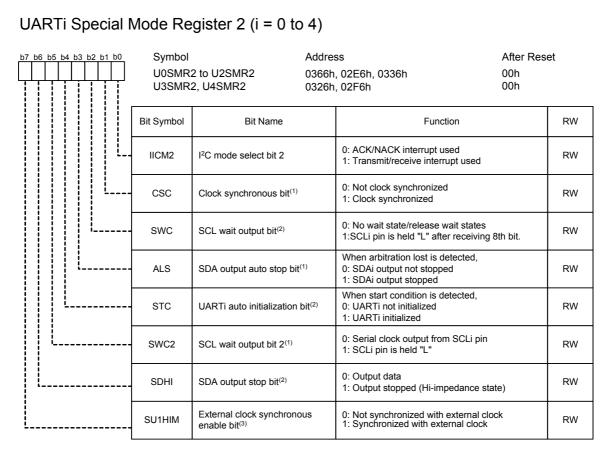

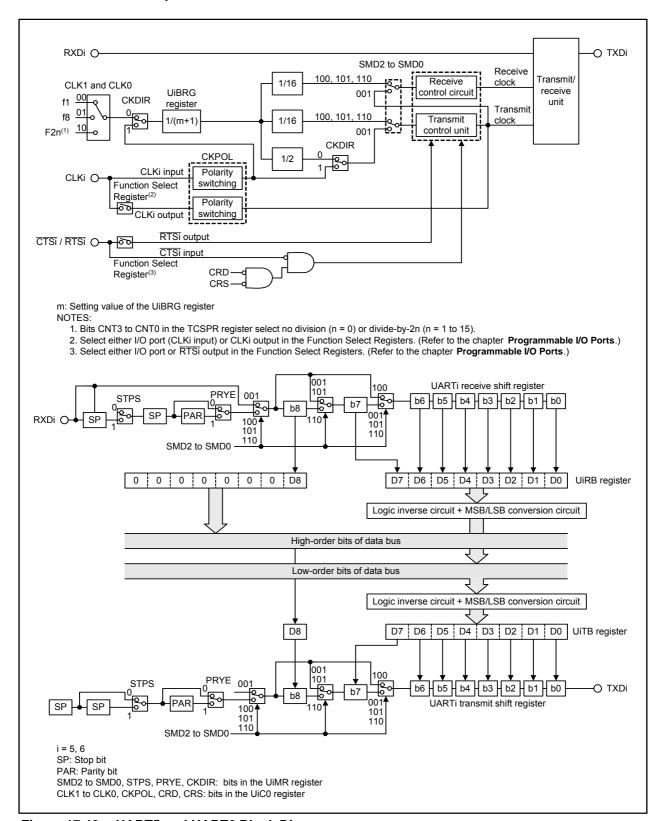

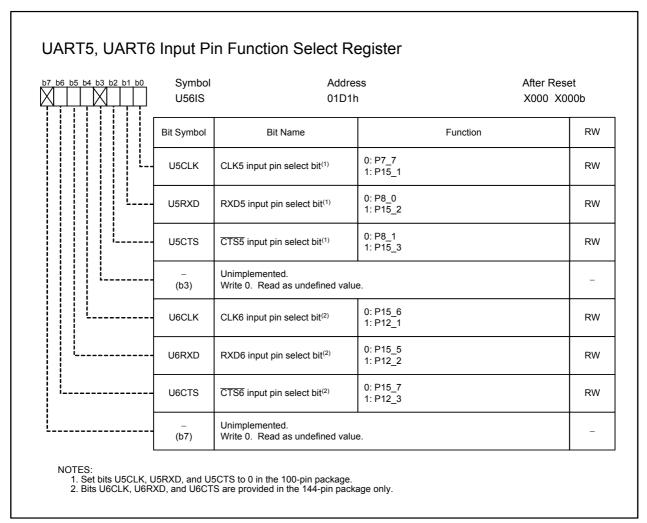

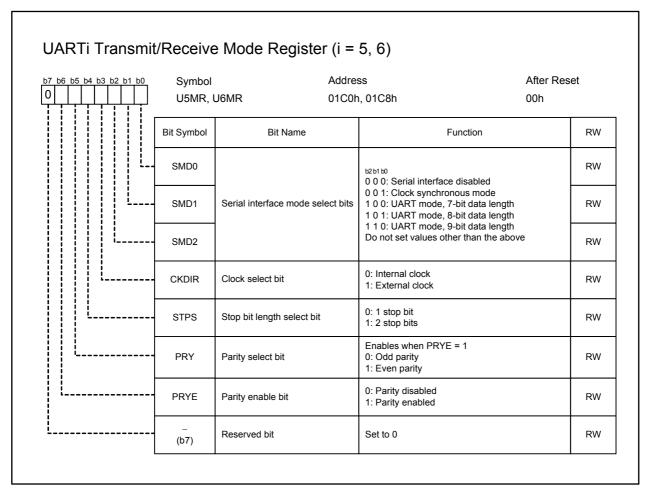

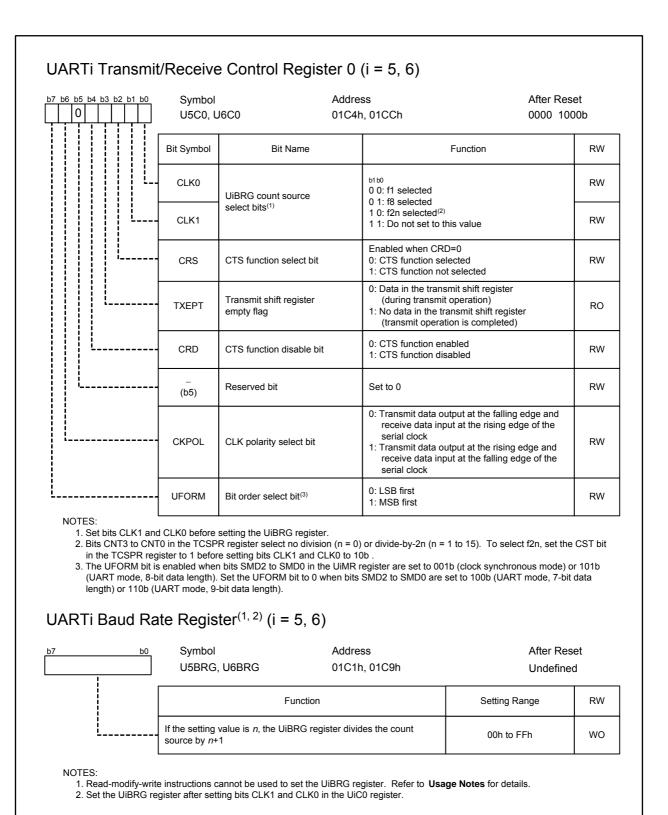

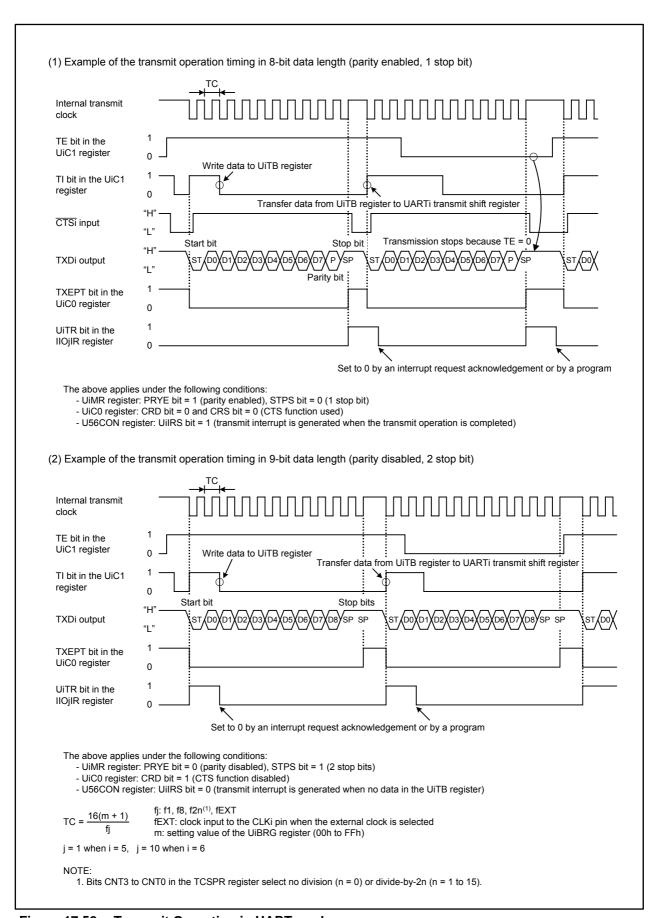

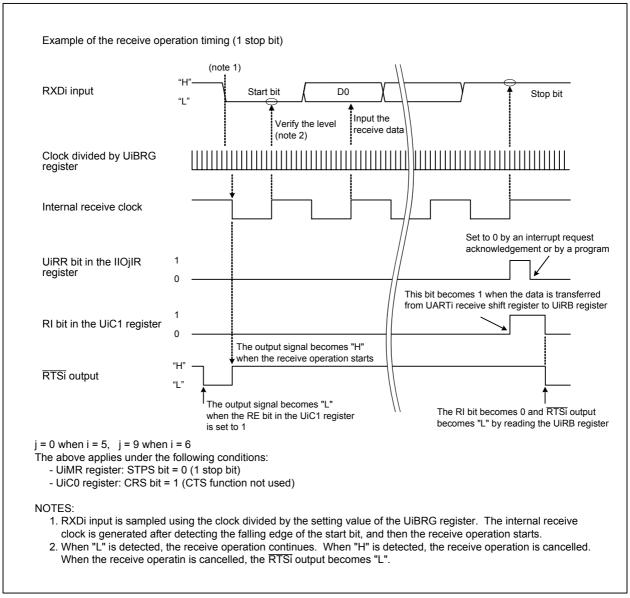

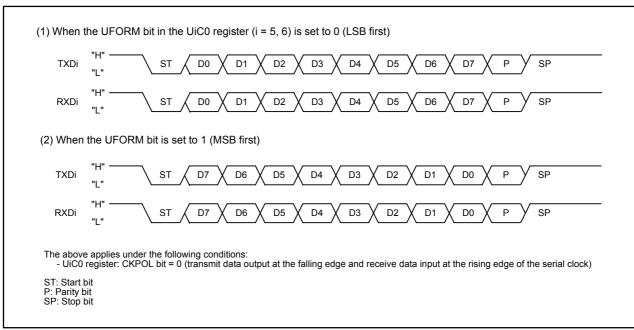

| 17. Se  | rial Interfaces                                                    | 214 |

| 17.1    | UART0 to UART4                                                     |     |

| 17.1.1  |                                                                    |     |

| 17.1.2  | •                                                                  |     |

| 17.1.3  | ·                                                                  |     |

| 17.1.4  | •                                                                  |     |

| 17.1.5  | •                                                                  |     |

| 17.1.6  | •                                                                  |     |

| 17.1.7  | •                                                                  |     |

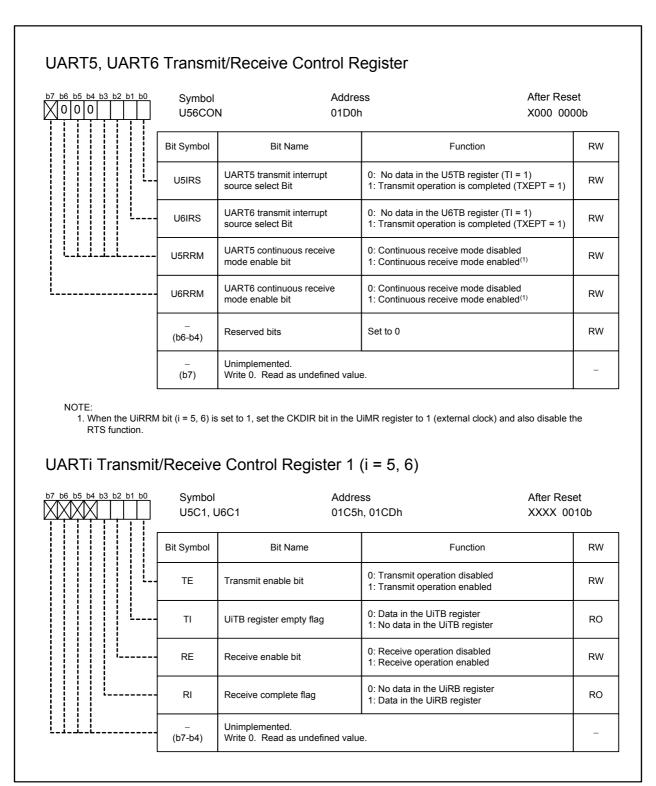

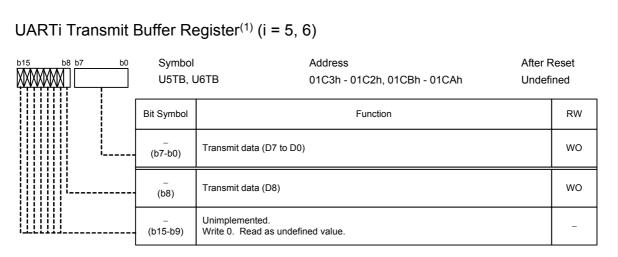

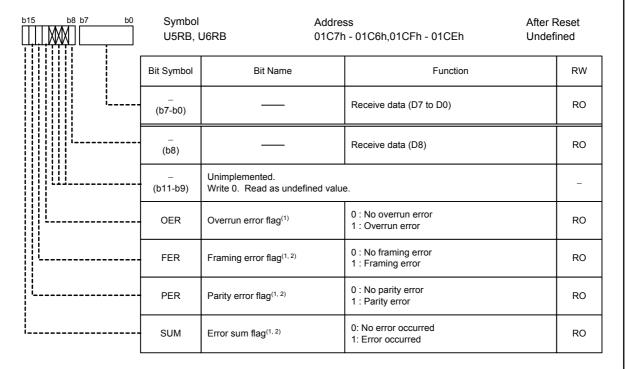

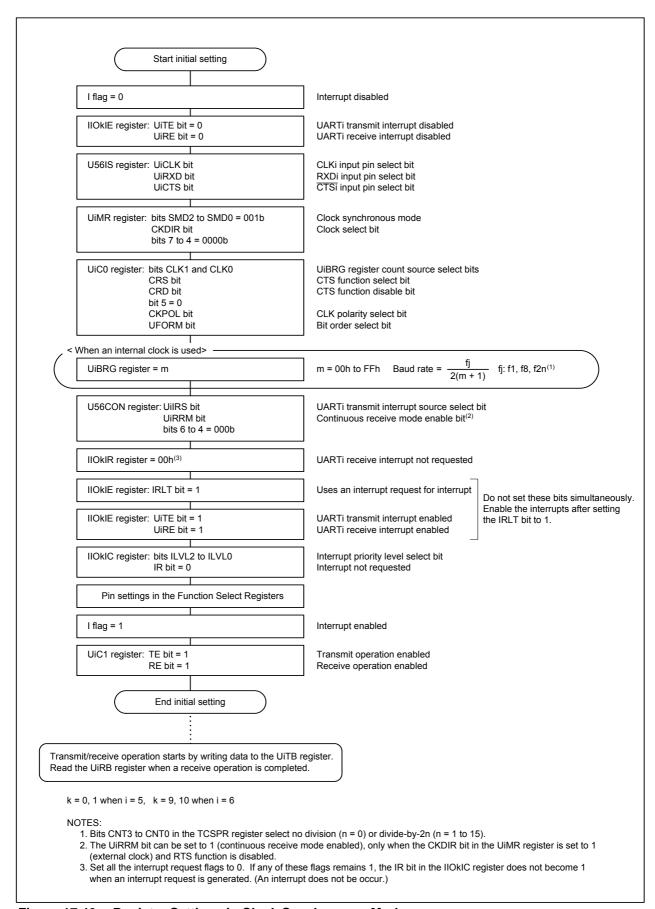

| 17.2    | UART5 and UART6                                                    |     |

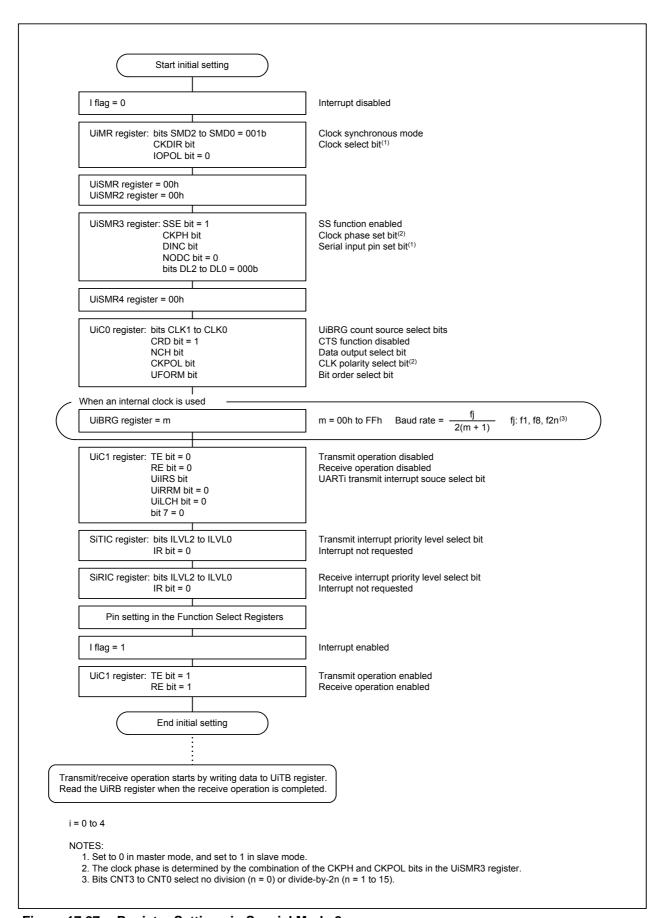

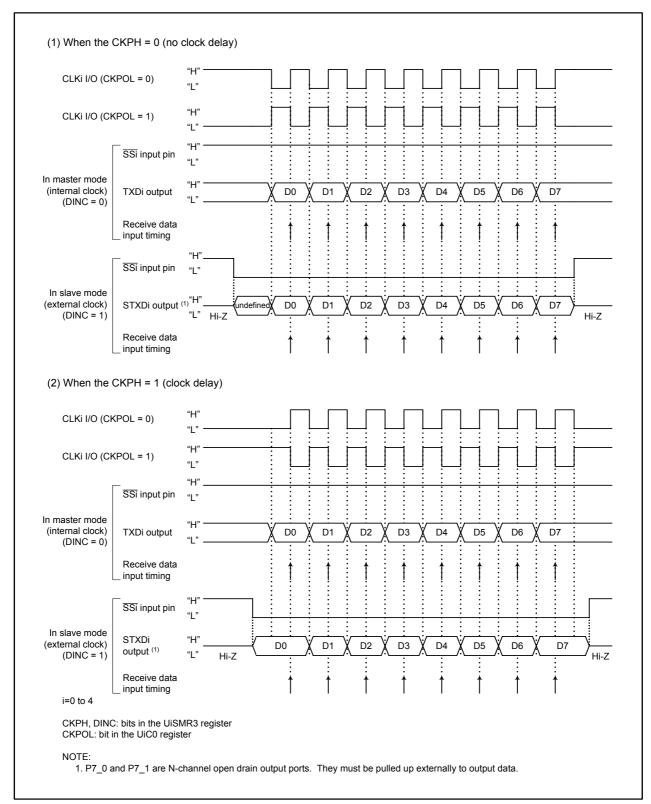

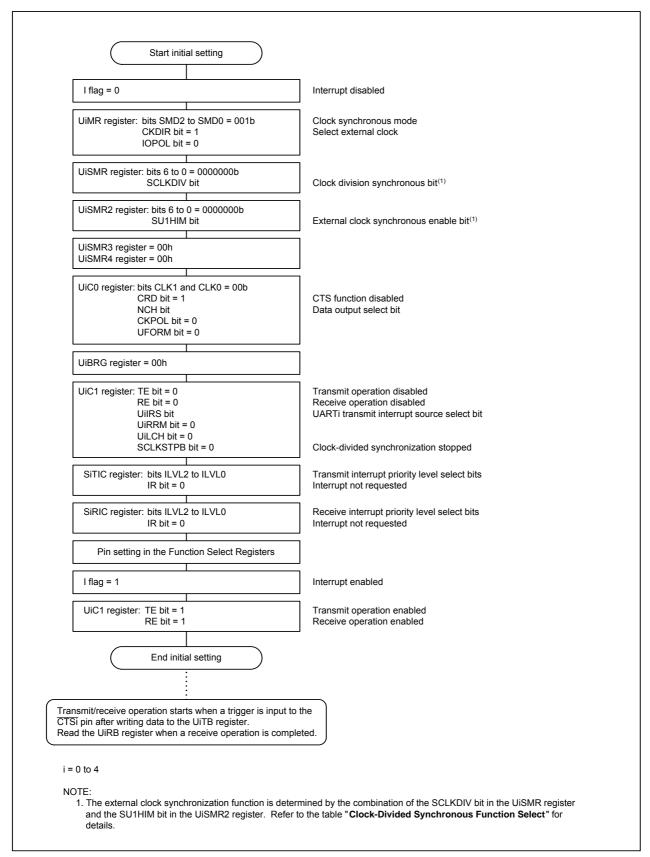

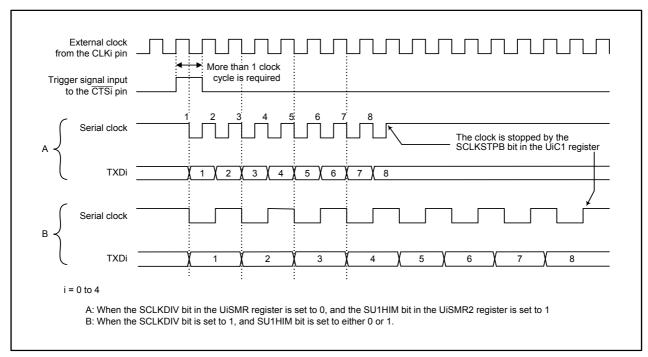

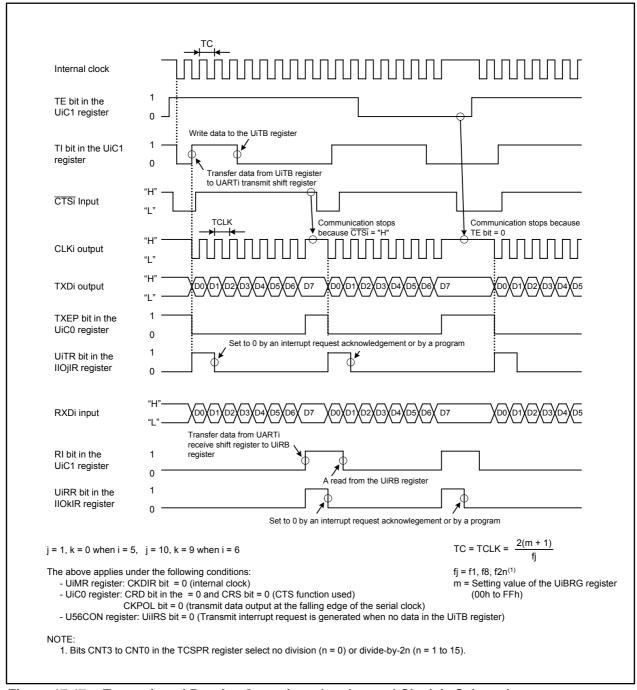

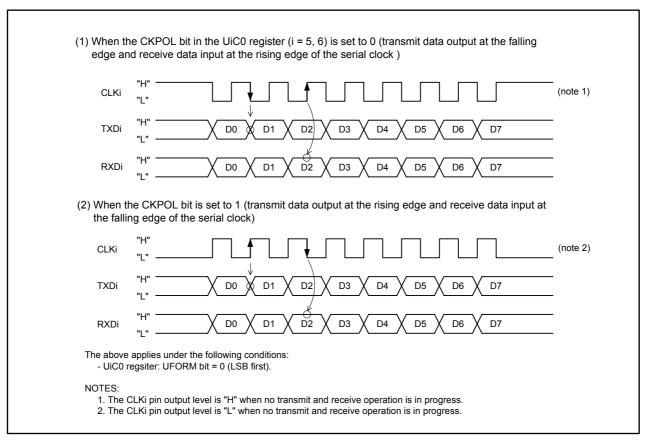

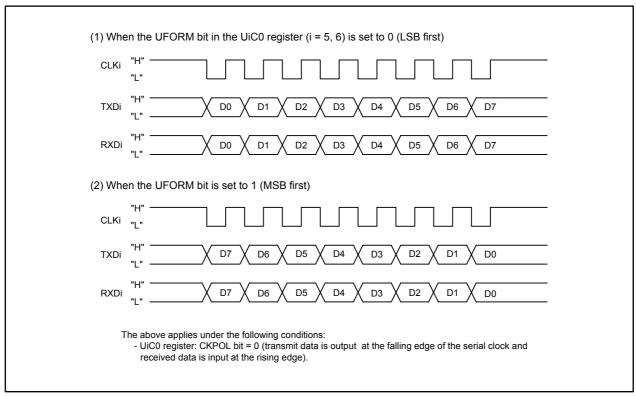

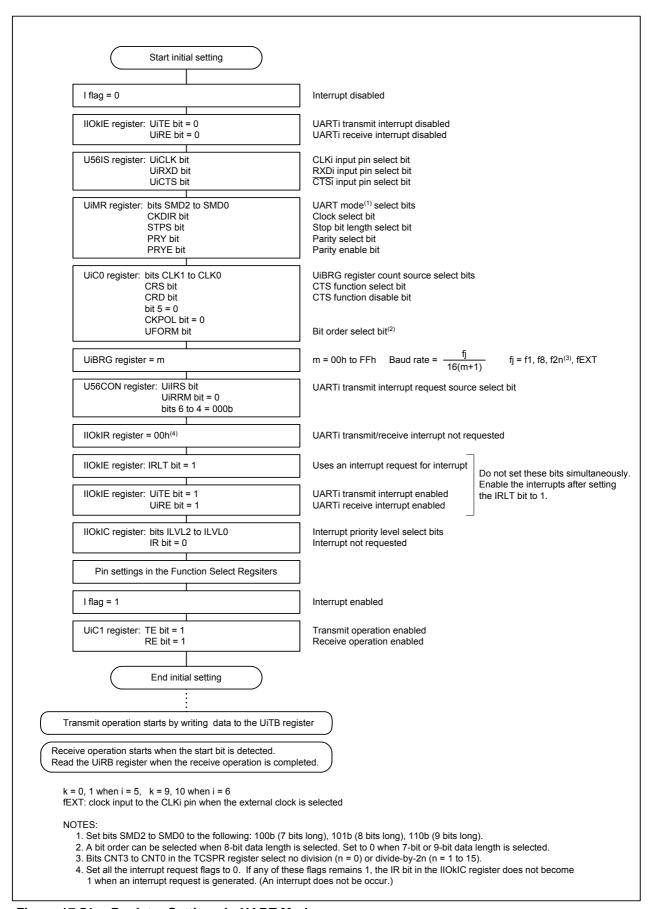

| 17.2.1  | Clock Synchronous Mode                                             | 278 |

| 17.2.2  | Clock Asynchronous (UART) Mode                                     | 286 |

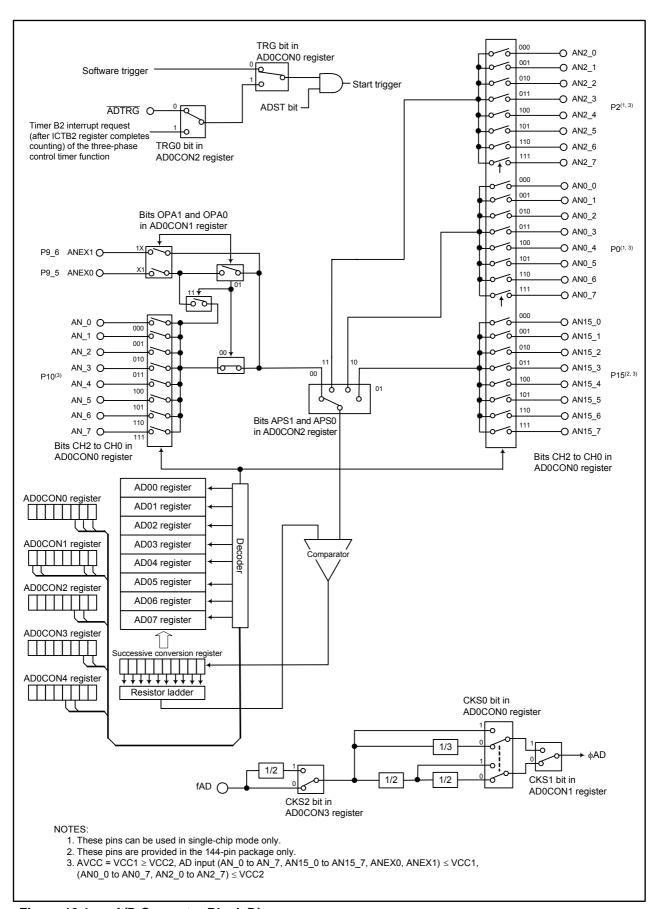

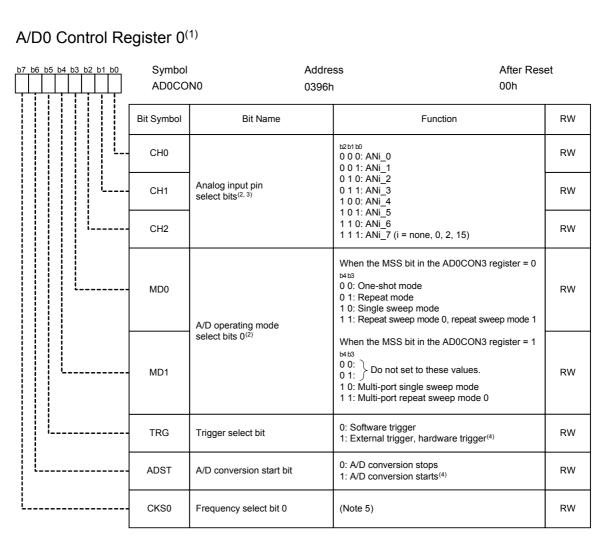

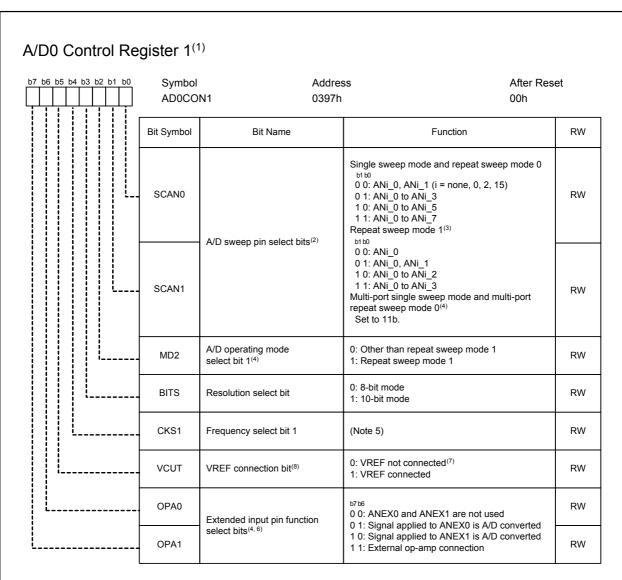

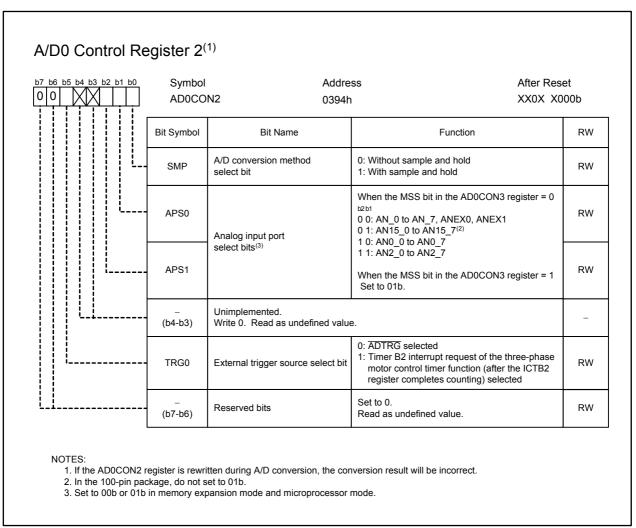

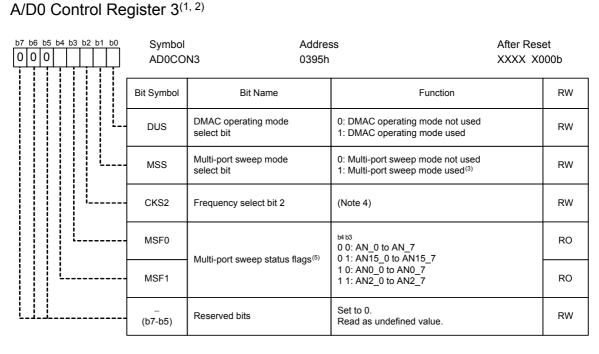

| 18. A/E | O Converter                                                        | 293 |

| 18.1    | Mode Descriptions                                                  |     |

| 18.1.1  | One-Shot Mode                                                      | 301 |

| 18.1.2  | Repeat Mode                                                        | 302 |

| 18.1.3  | Single Sweep Mode                                                  | 303 |

| 18.1.4  | Repeat Sweep Mode 0                                                | 304 |

| 18.1.5  | Repeat Sweep Mode 1                                                | 305 |

| 18.1.6  | Multi-Port Single Sweep Mode                                       | 307 |

| 18.1.7  | Multi-Port Repeat Sweep Mode 0                                     | 308 |

| 18.2    | Functions                                                          | 309 |

| 18.2.1  | Resolution                                                         | 309 |

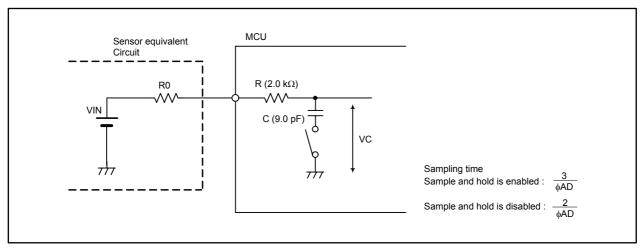

| 18.2.2  | Sample and Hold                                                    | 309 |

| 18.2.3  | Trigger Select Function                                            | 309 |

| 18.2.4  |                                                                    |     |

| 18.2.5  | Extended Analog Input Pins                                         | 309 |

| 18.2.6       | External Operating Amplifier (Op-Amp) Connection Mode                                  | 310 |

|--------------|----------------------------------------------------------------------------------------|-----|

| 18.2.7       | Power Consumption Reduce Function                                                      | 310 |

| 18.3 Re      | and from the AD0i Register ( $i = 0$ to 7)                                             | 311 |

| 18.4 Ou      | tput Impedance of Sensor Equivalent Circuit under A/D Conversion                       | 311 |

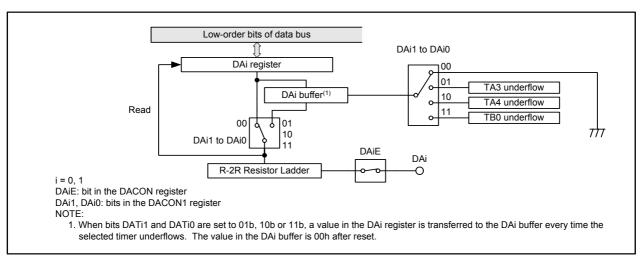

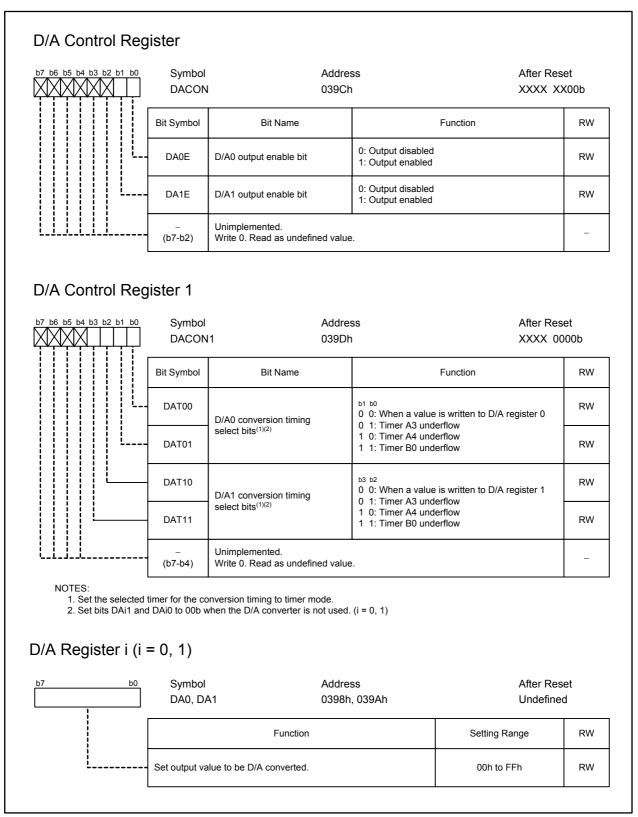

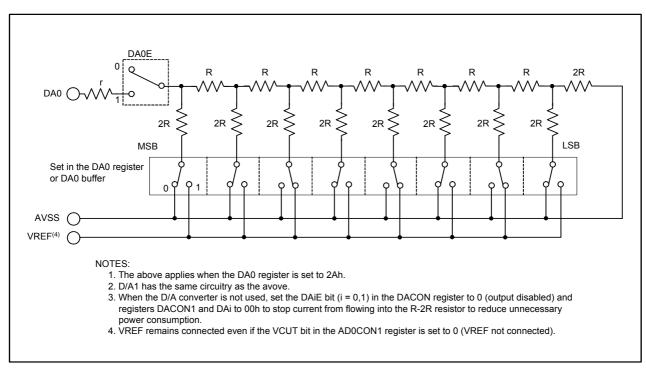

| 19. D/A Co   | onverter                                                                               | 313 |

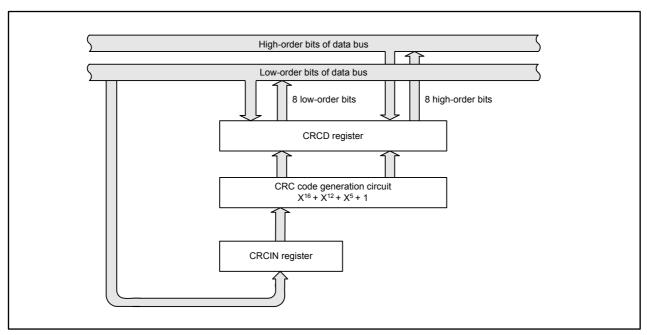

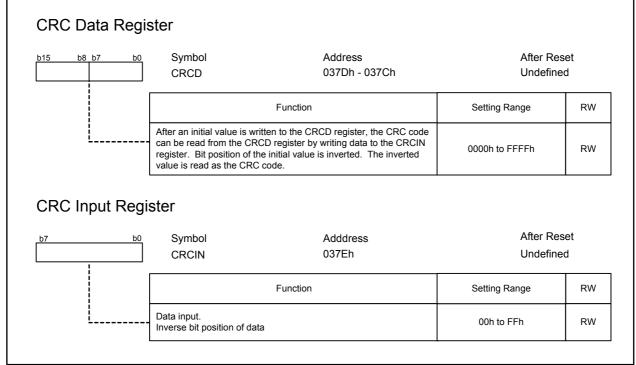

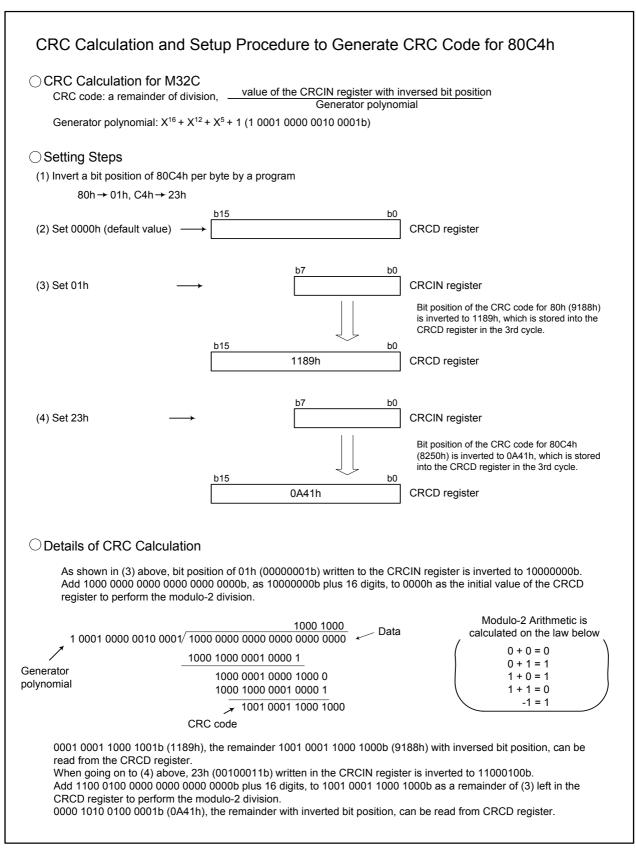

| 20. CRC C    | alculation                                                                             | 316 |

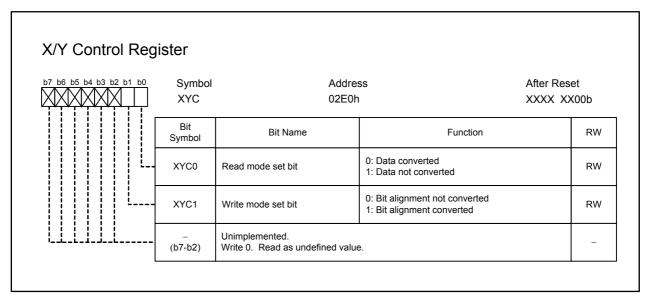

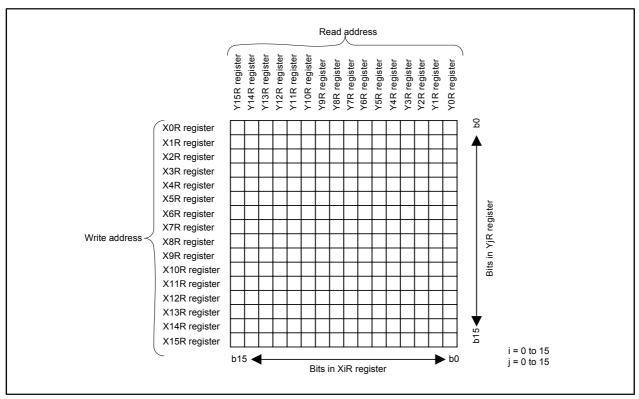

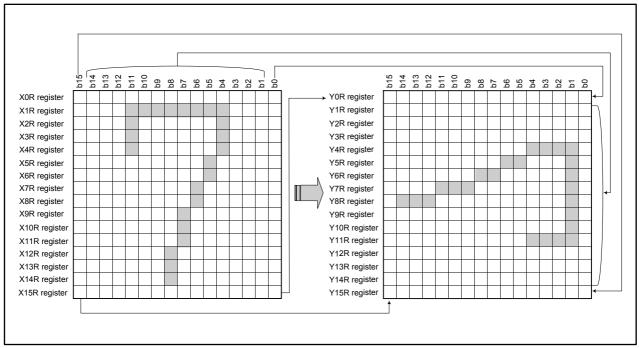

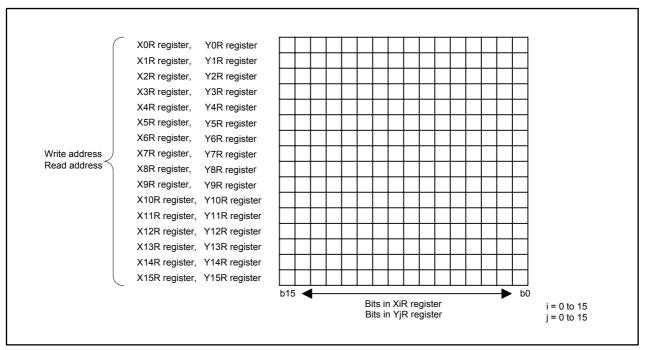

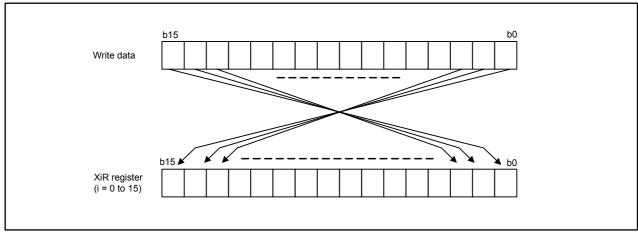

| 21. X/Y Co   | nversion                                                                               | 318 |

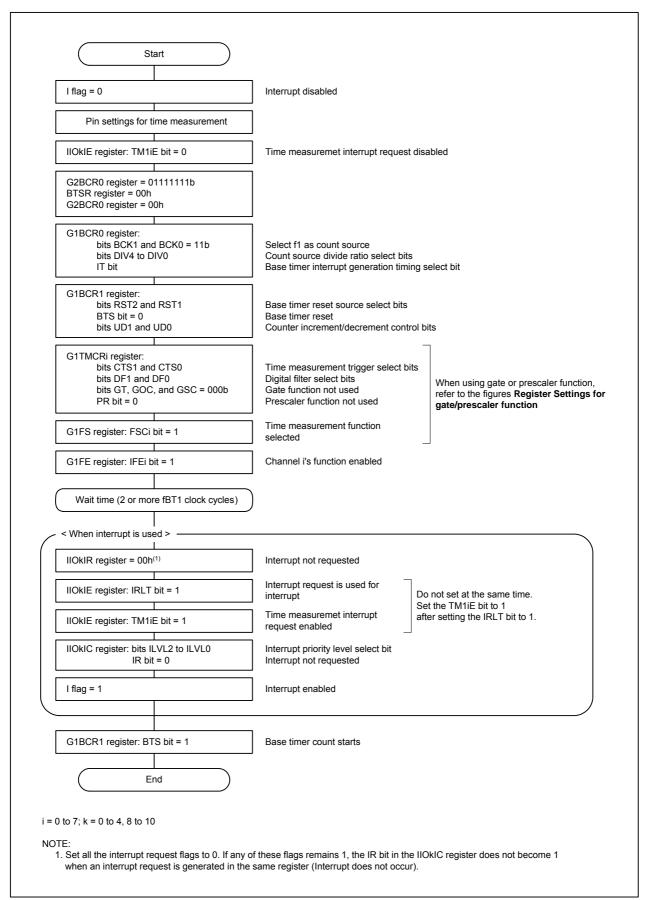

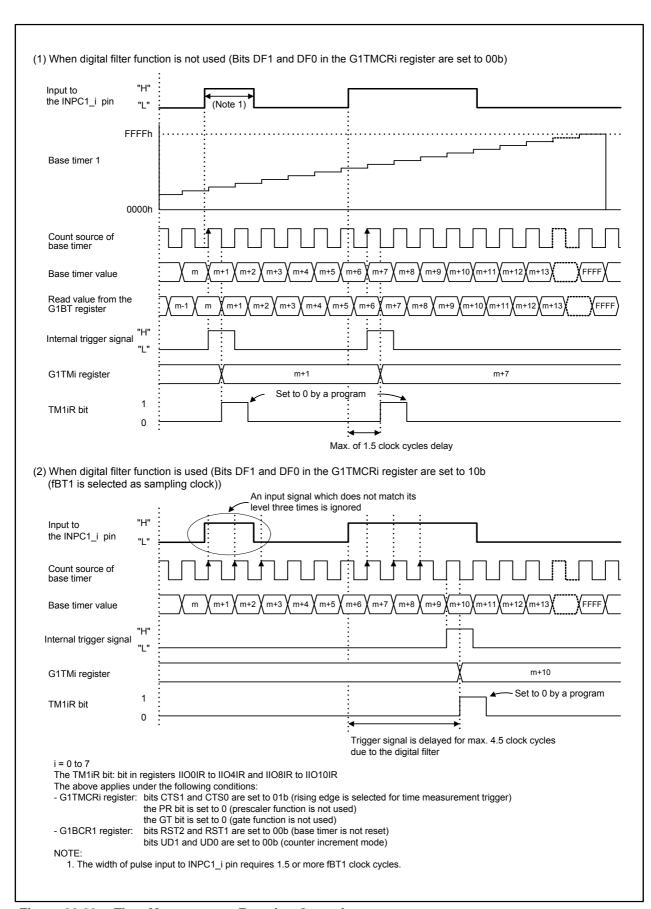

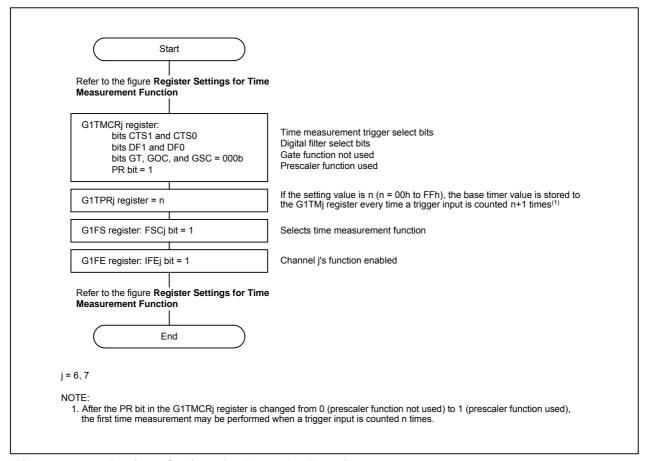

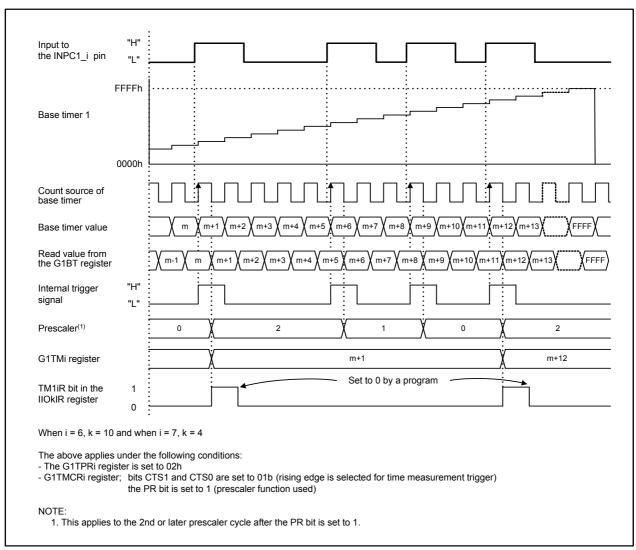

| 22. Intellig | ent I/O                                                                                | 321 |

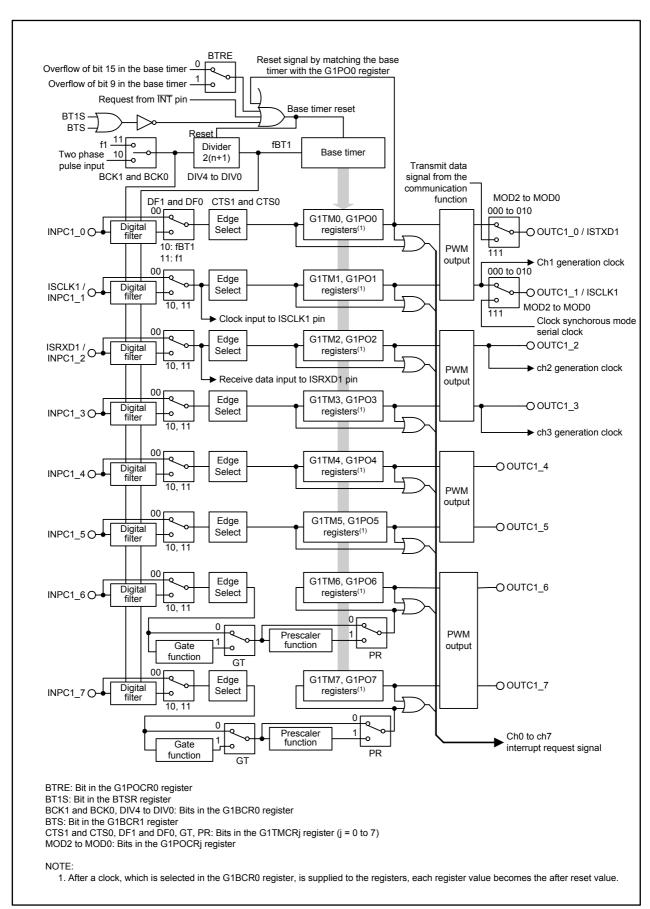

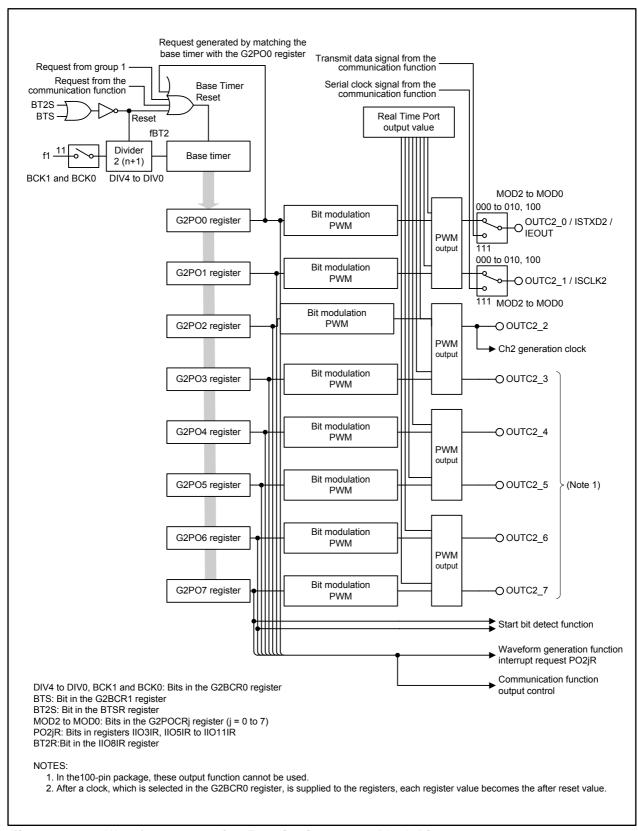

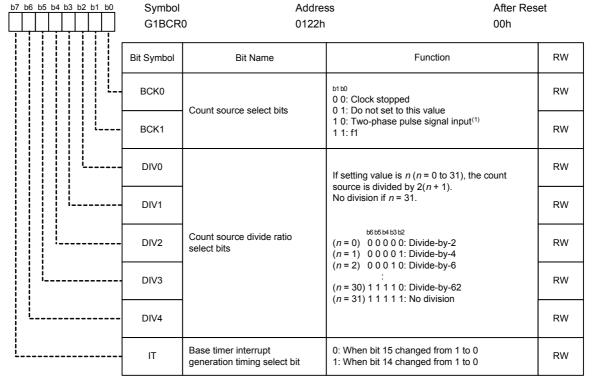

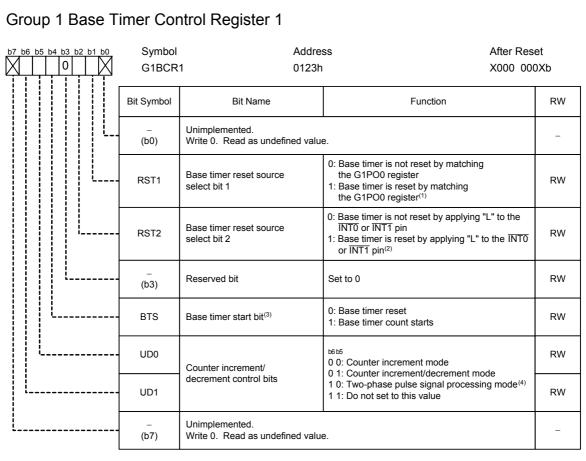

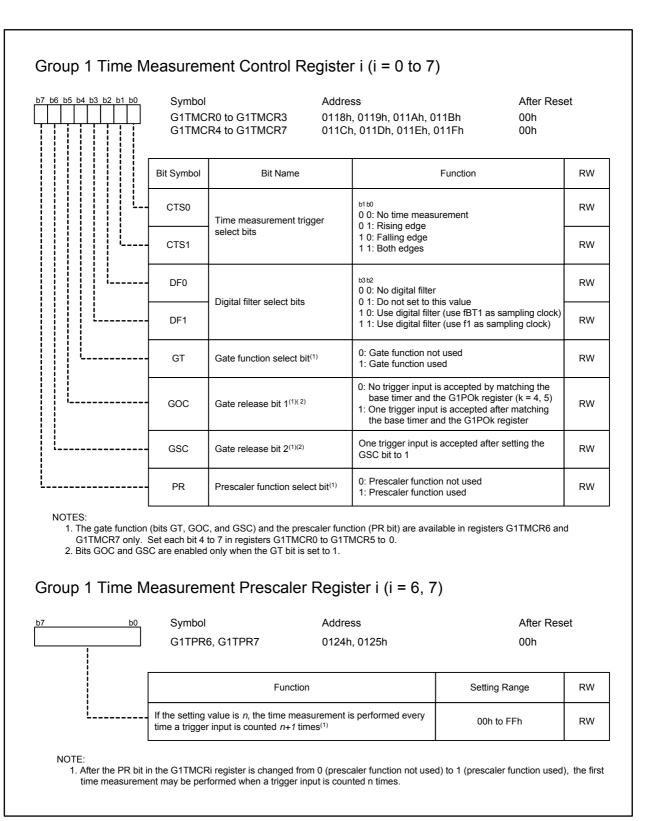

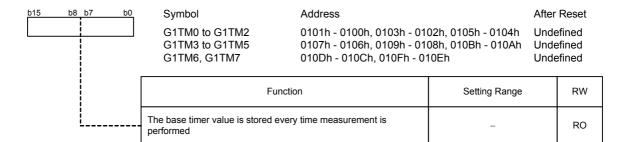

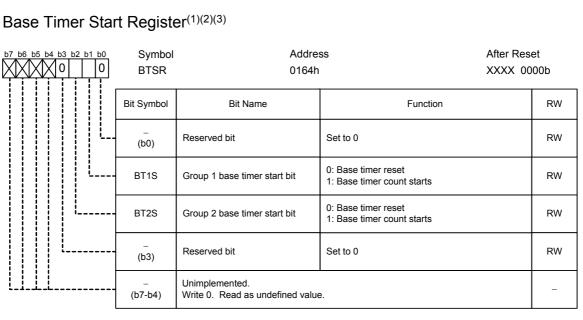

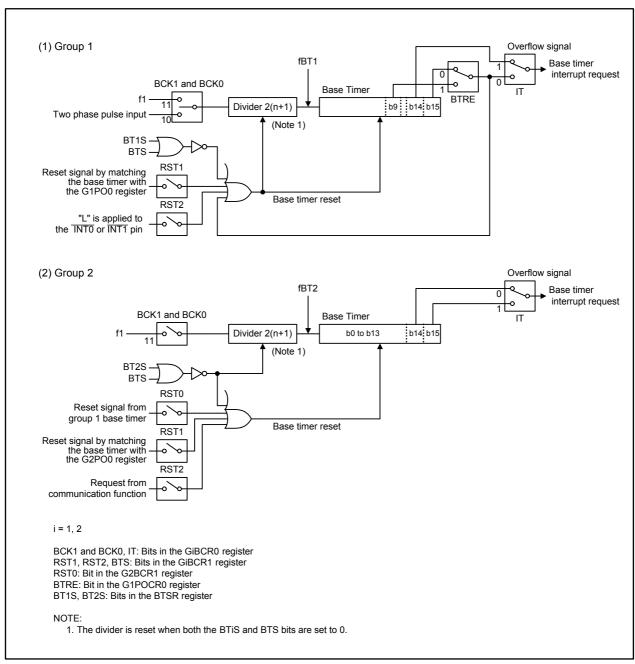

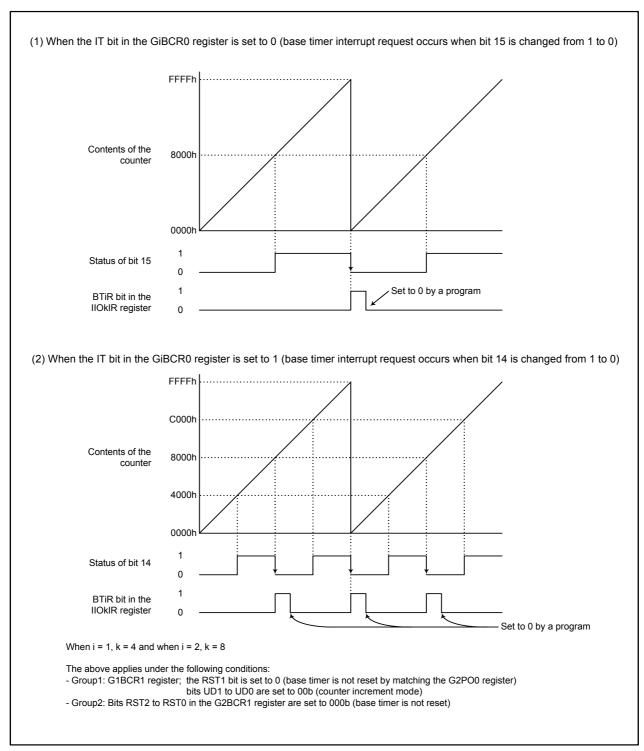

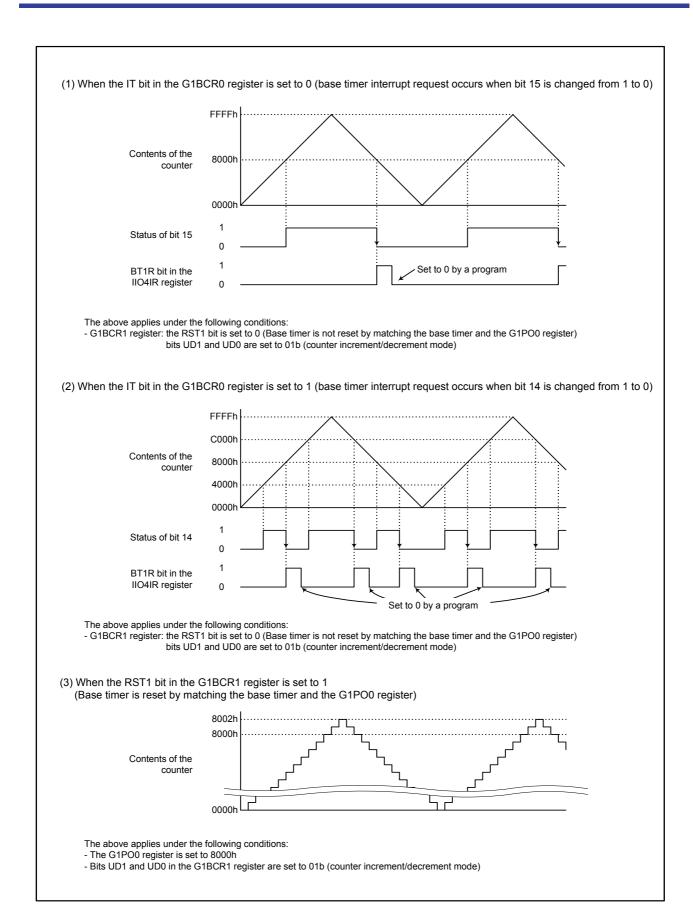

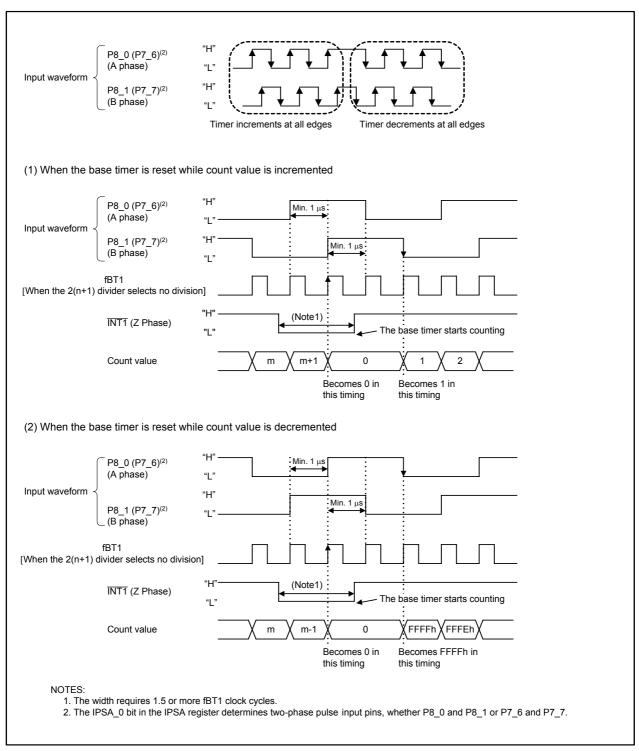

| 22.1 Ba      | se Timer                                                                               | 336 |

|              | ne Measurement Function (Input Capture)                                                |     |

|              | Prescaler Function                                                                     |     |

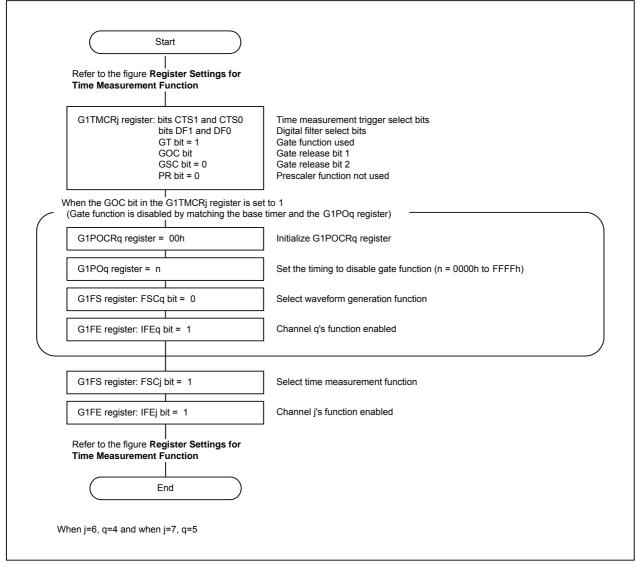

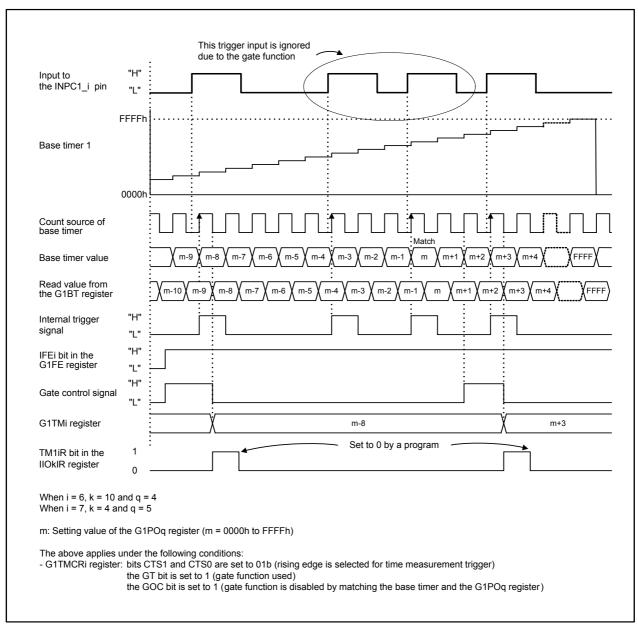

| 22.2.2       | Gate Function                                                                          | 348 |

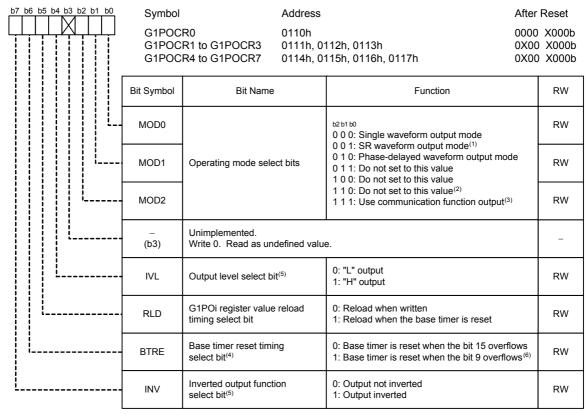

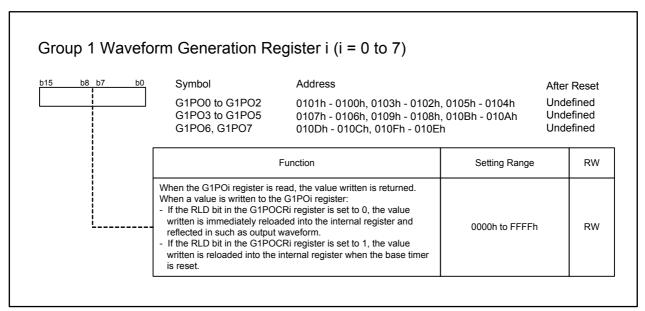

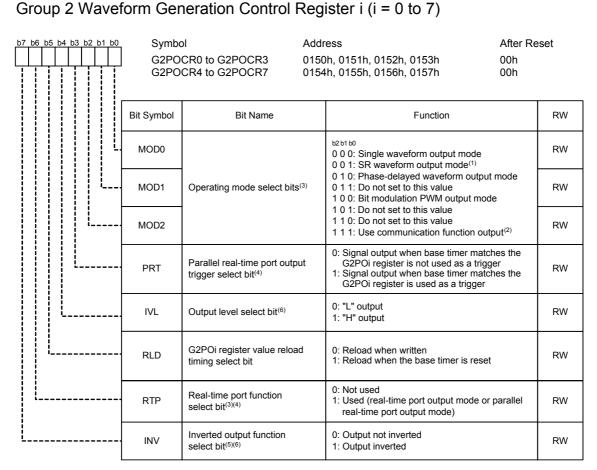

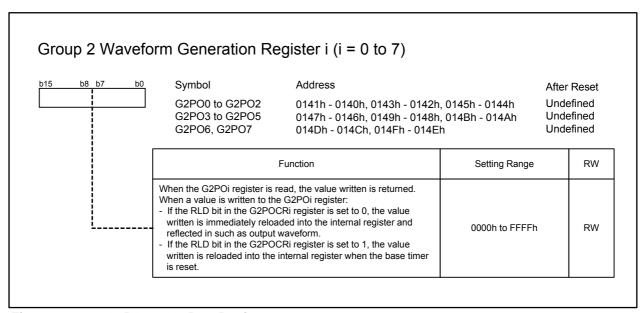

|              | veform Generation Function (Output Compare)                                            |     |

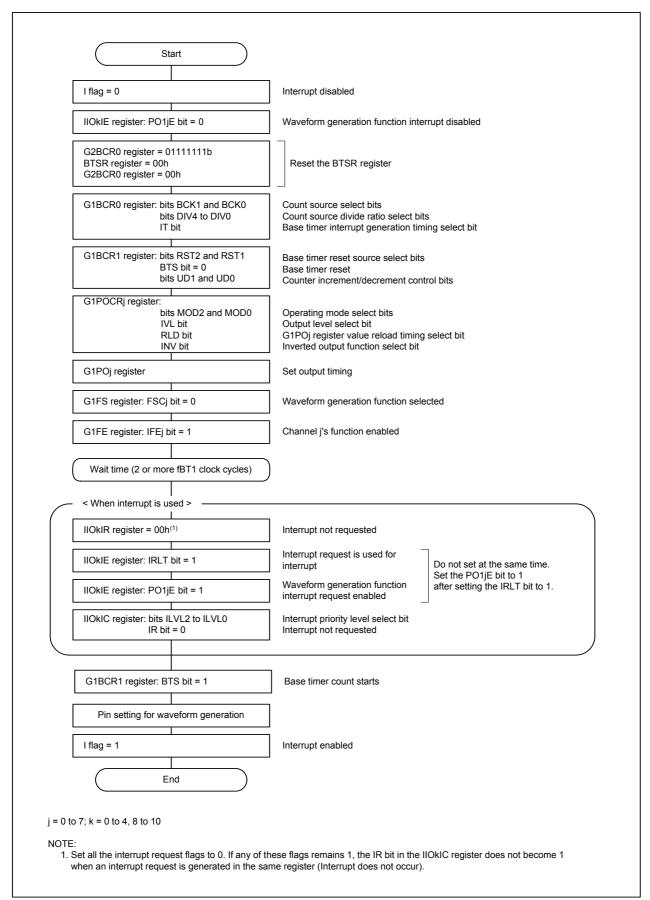

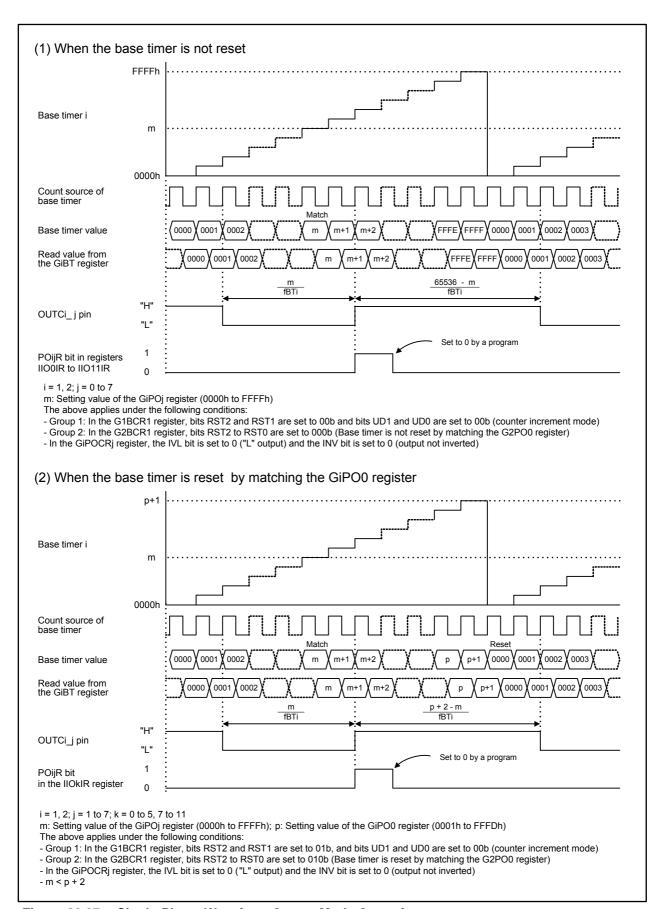

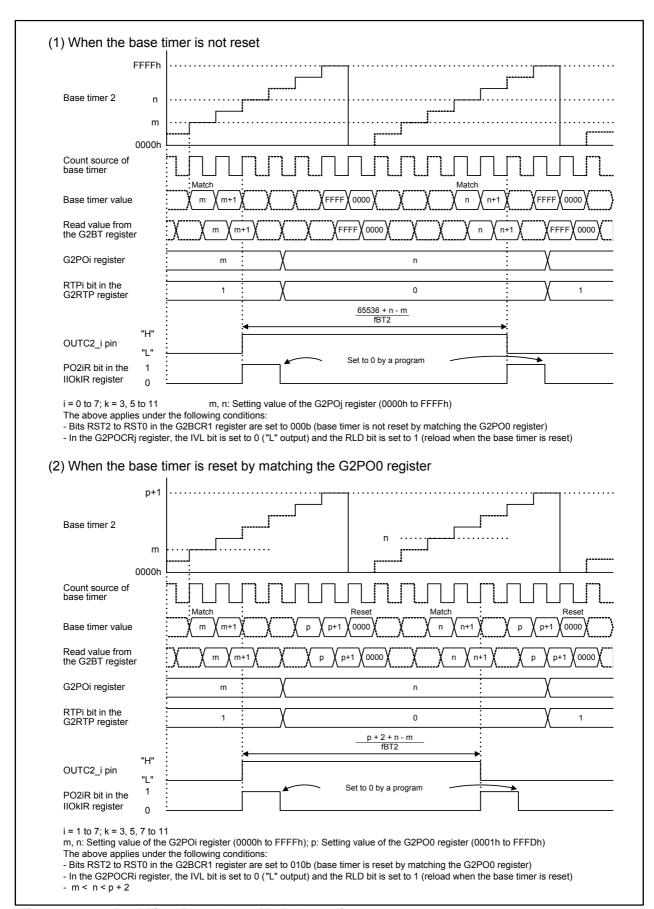

|              | Single-Phase Waveform Output Mode (Group 1 and Group 2)                                |     |

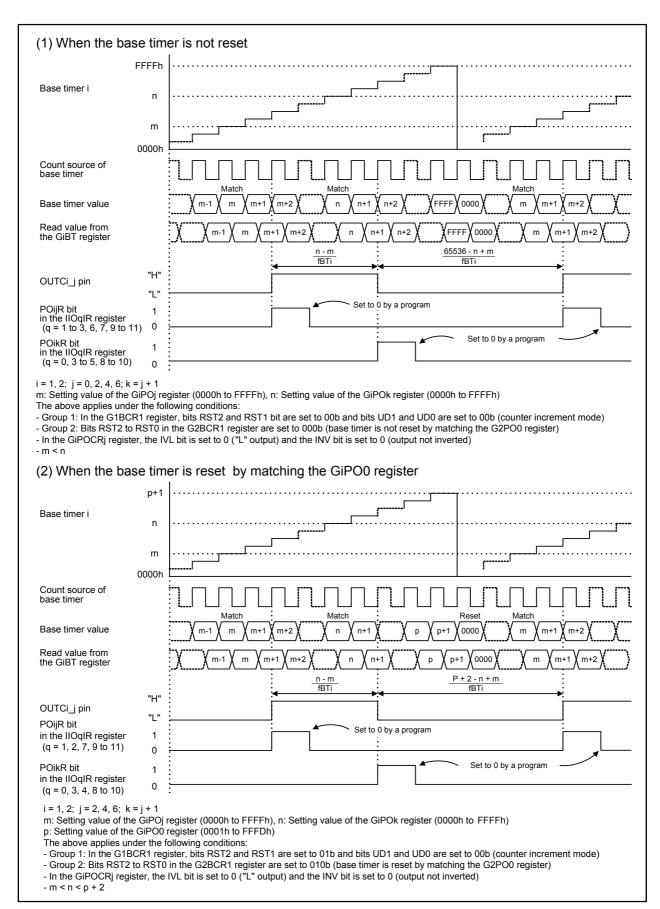

|              | Phase-Delayed Waveform Output Mode (Group 1 and Group 2)                               |     |

|              | Set/Reset (SR) Waveform Output Mode (Group 1 and Group 2)                              |     |

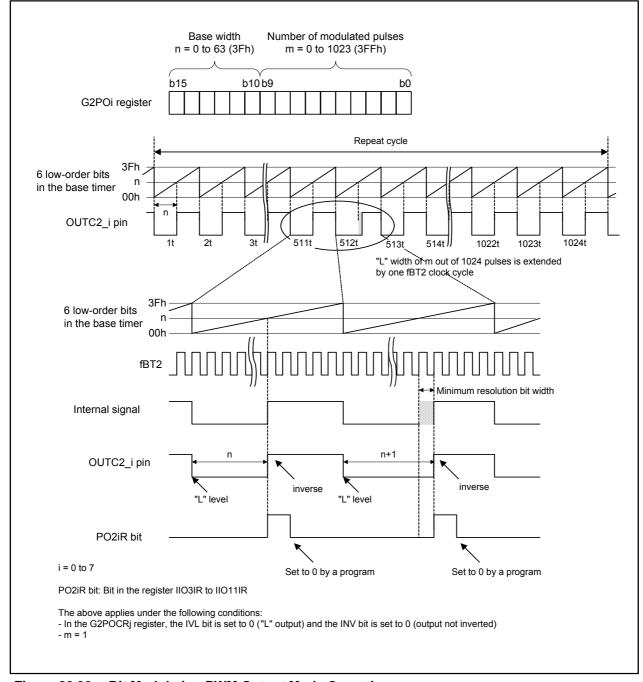

| 22.3.4       | Bit Modulation PWM Output Mode (Group 2)                                               | 360 |

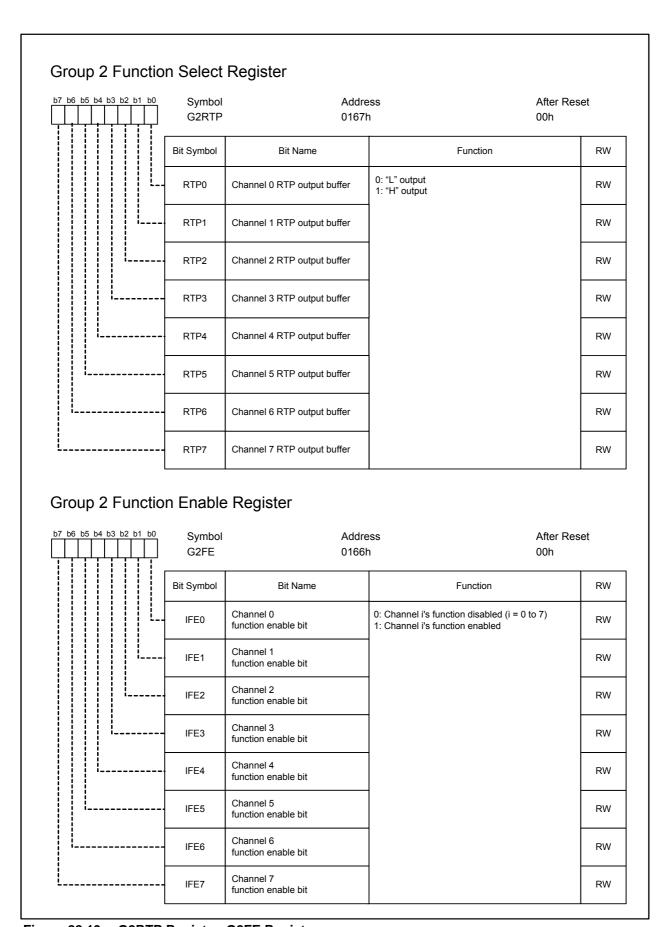

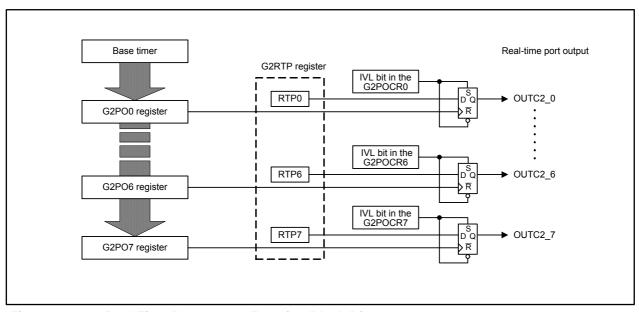

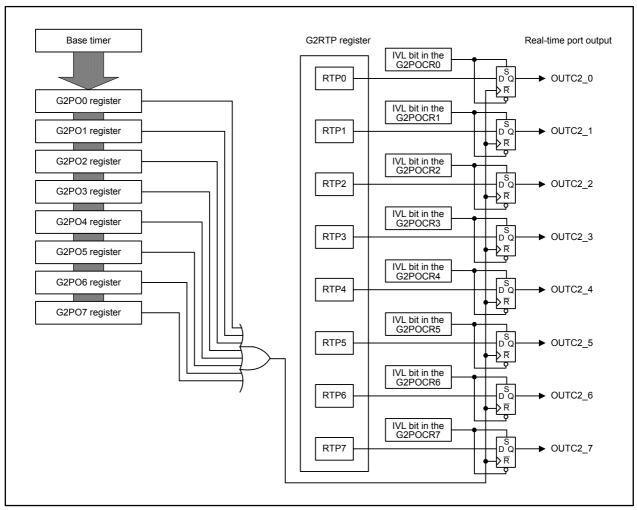

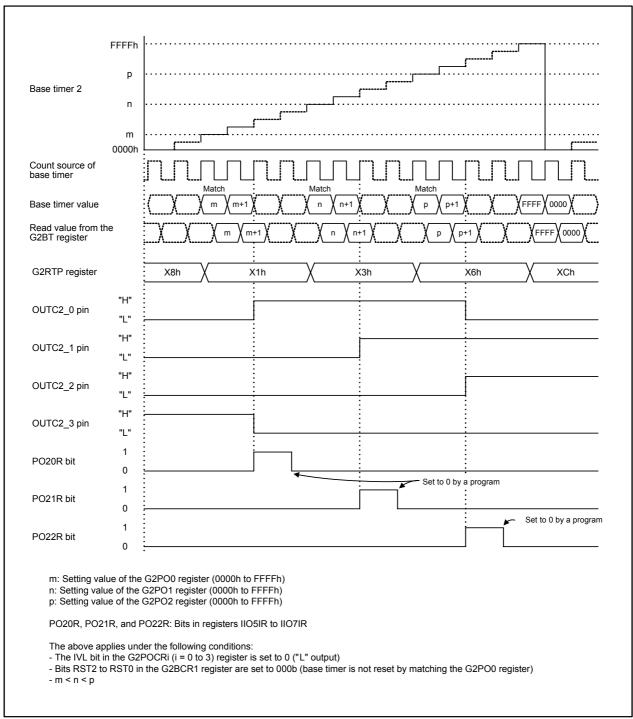

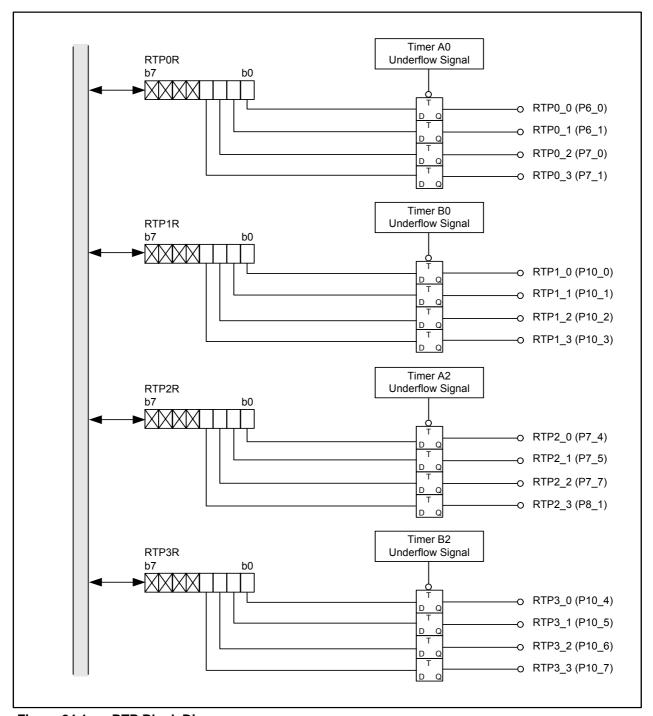

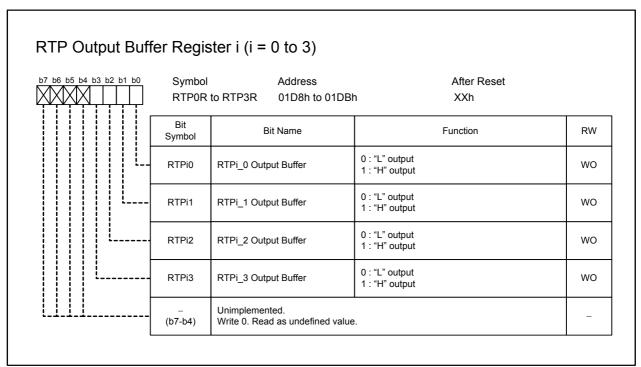

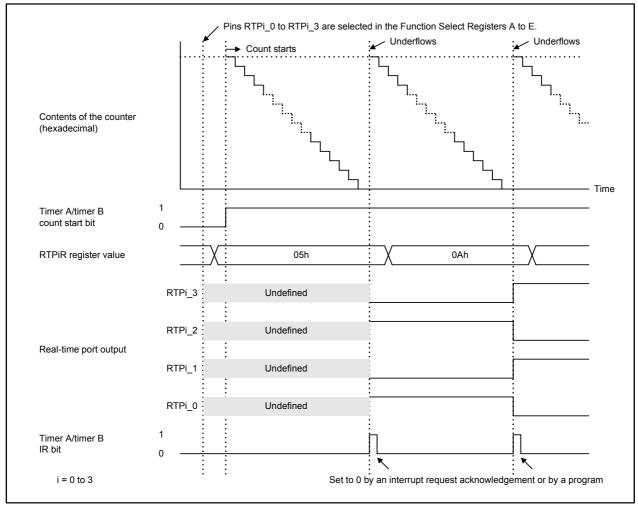

| 22.3.5       | Real-Time Port Output Mode (Group 2)                                                   | 362 |

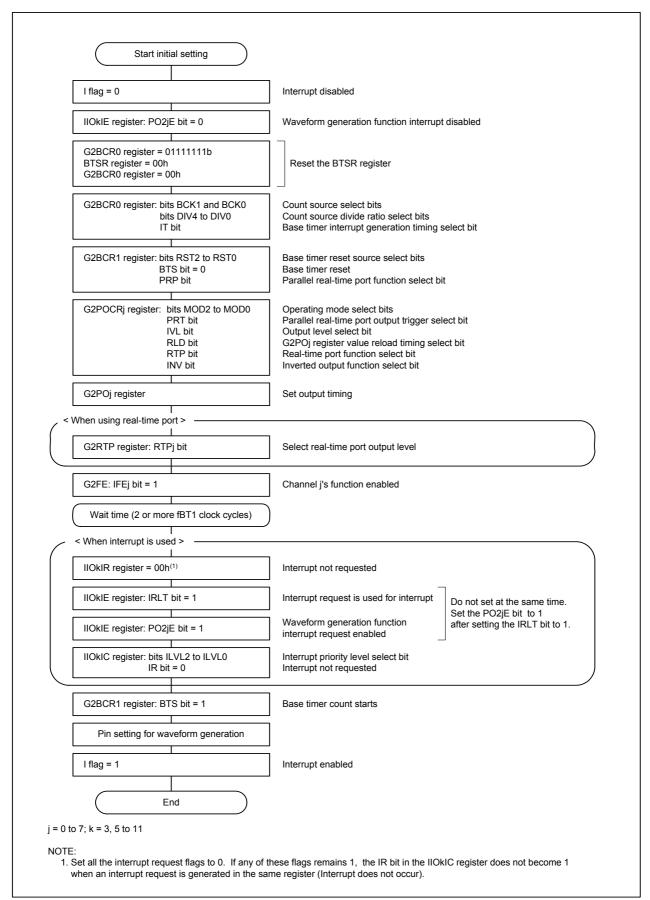

| 22.3.6       | Parallel Real-Time Port Output Mode (Group 2)                                          | 364 |

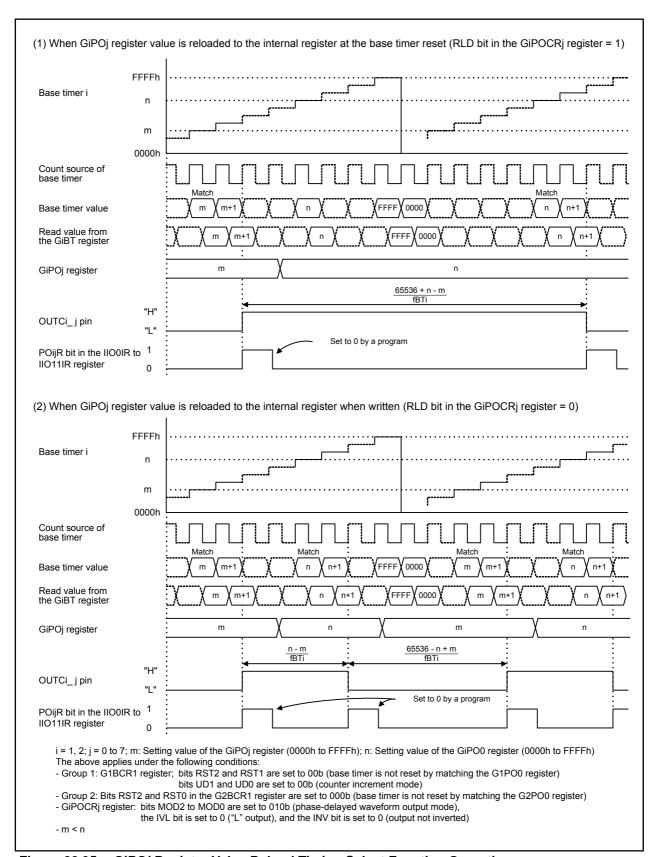

| 22.3.7       | GiPOj Register Value Reload Timing Select Function ( $i = 1, 2; j = 0 \text{ to } 7$ ) | 367 |

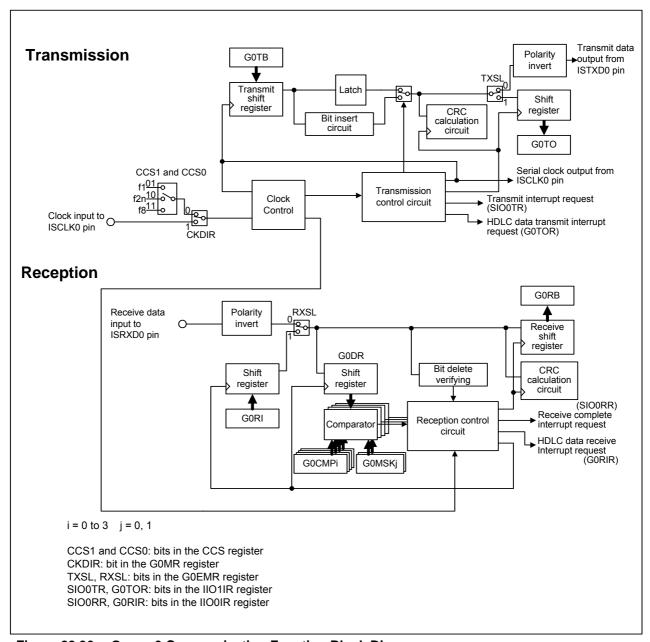

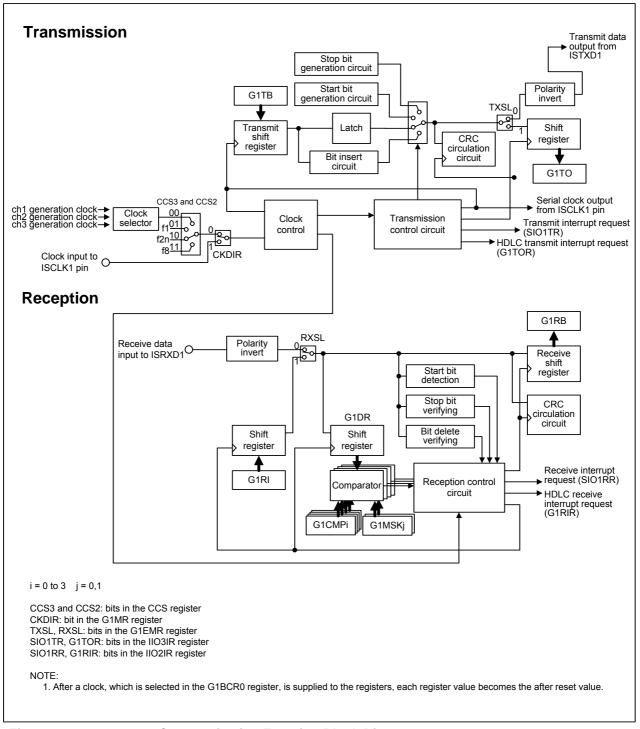

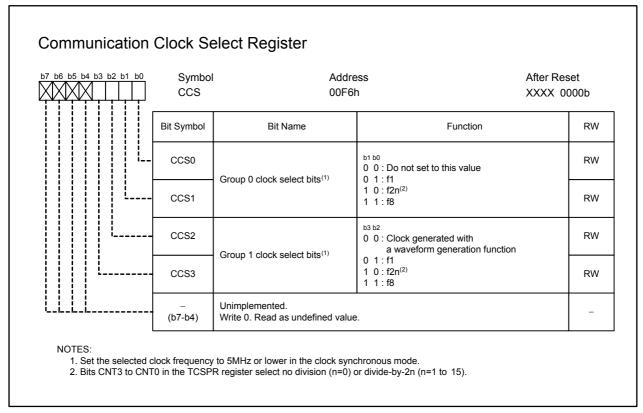

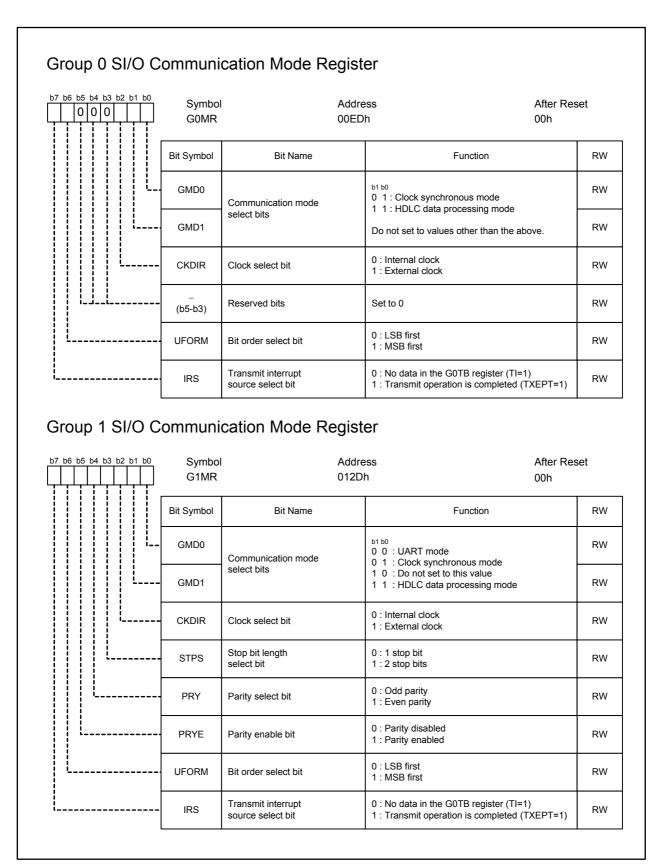

| 22.4 Gre     | oup 0 and Group 1 Communication Function                                               | 368 |

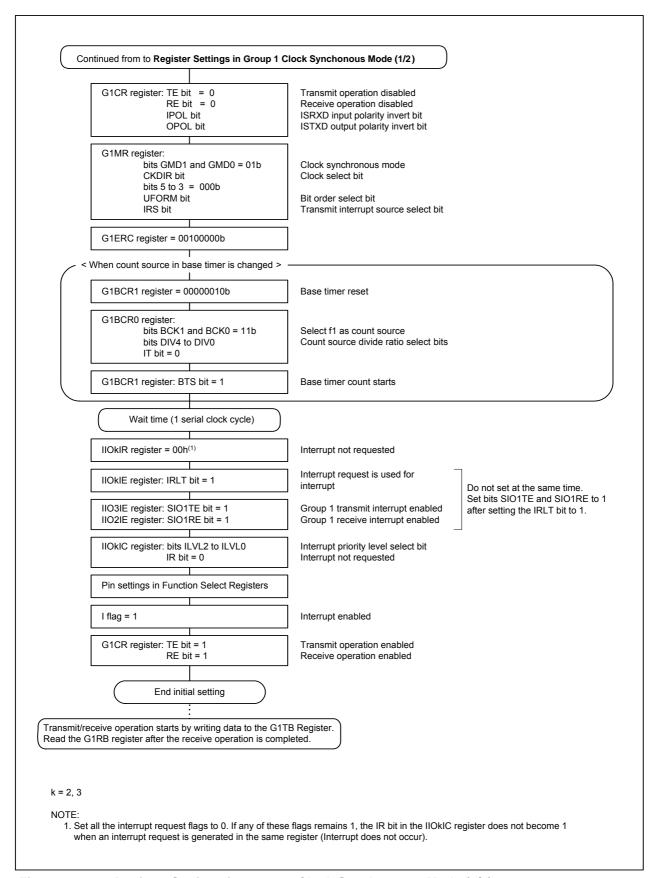

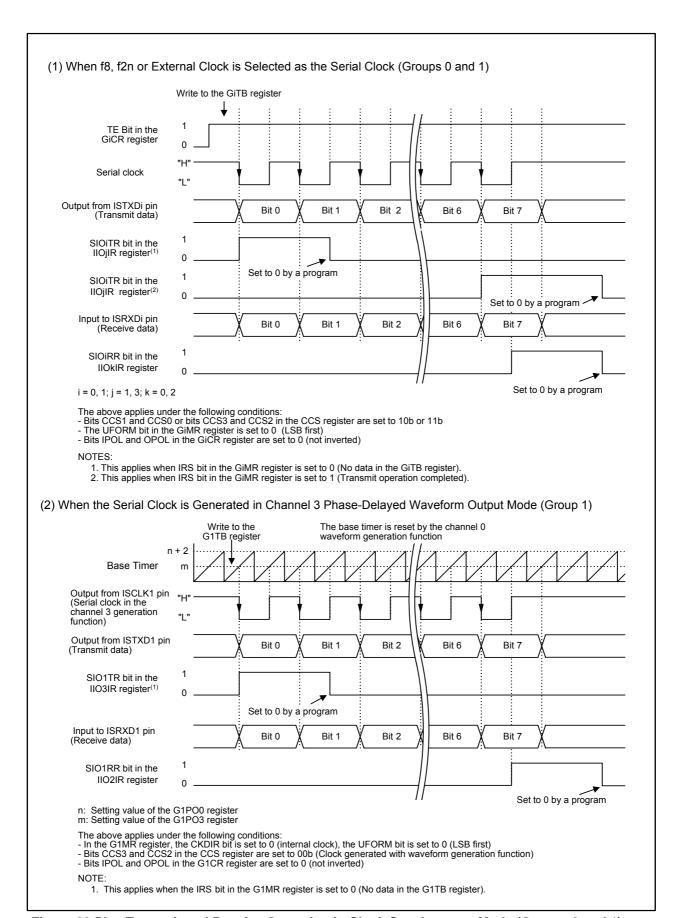

| 22.4.1       | Clock Synchronous Mode (Groups 0 and 1)                                                | 379 |

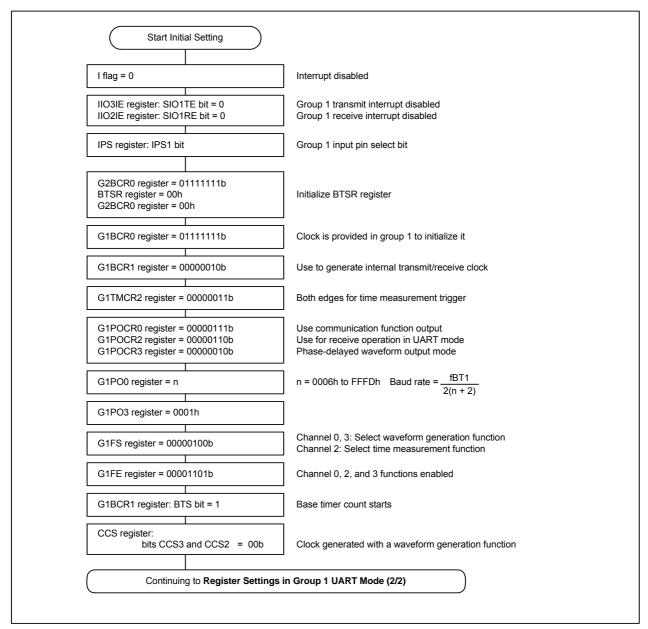

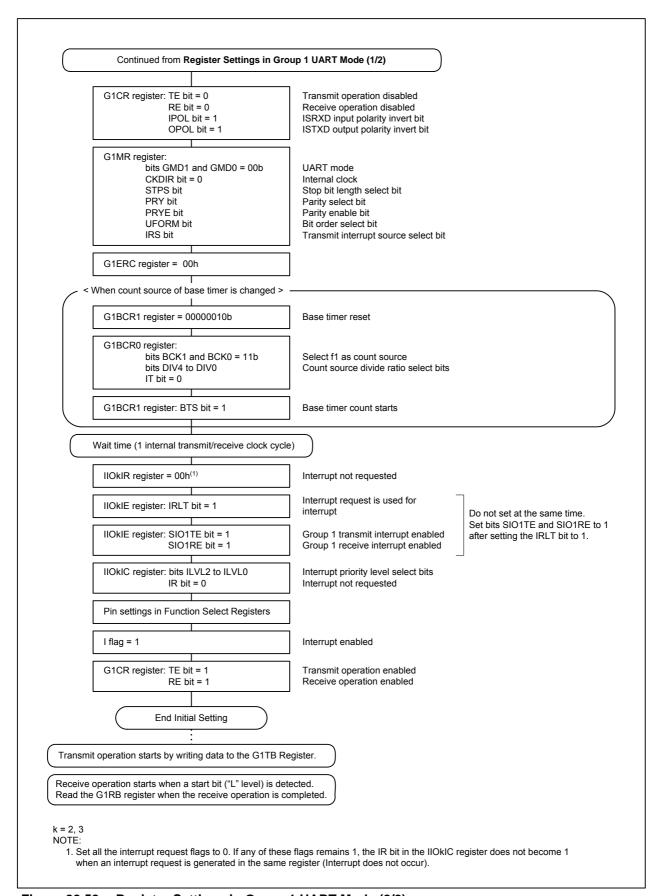

| 22.4.2       | Clock Asynchronous (UART) Mode (Group 1)                                               | 385 |

| 22.4.3       | HDLC Data Processing Mode (Group 0 and Group 1)                                        | 389 |

| 22.5 Gre     | oup 2 Communication Function                                                           | 392 |

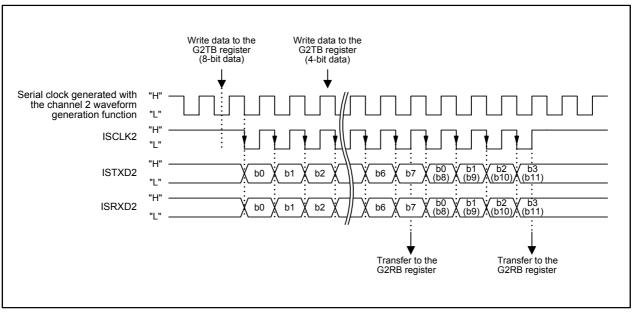

| 22.5.1       | Variable Data Length Clock Synchronous Mode (Group 2)                                  | 398 |

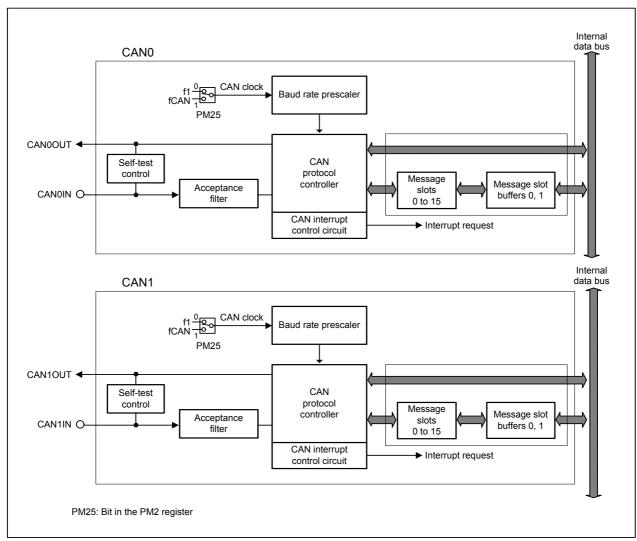

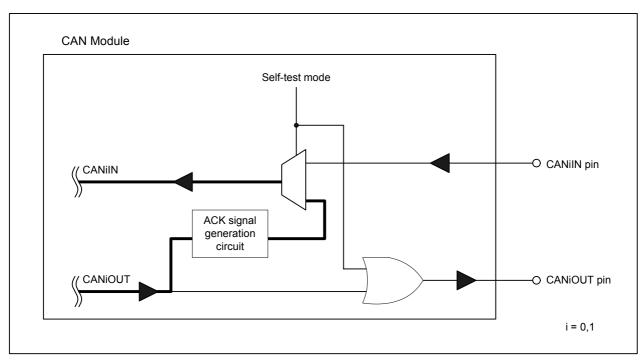

| 23. CAN M    | lodule                                                                                 | 401 |

| 23.1 CA      | N-Associated Registers                                                                 | 405 |

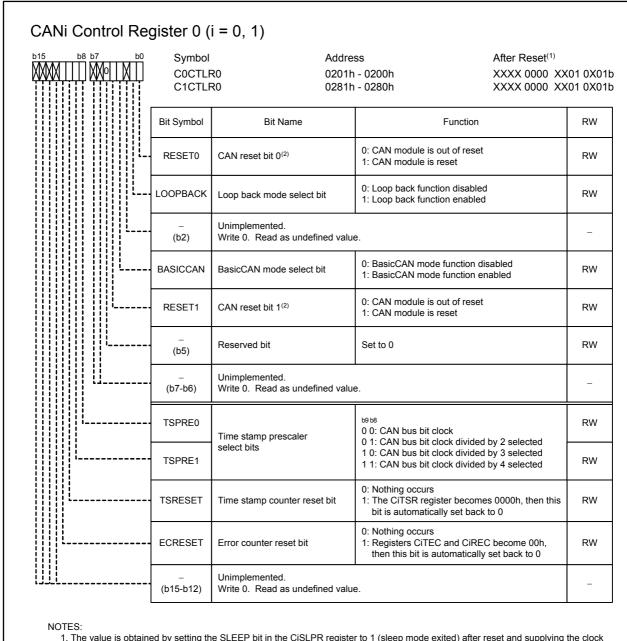

| 23.1.1       | CANi Control Register 0 (CiCTLR0 Register) (i = 0, 1)                                  | 405 |

|              | CANi Control Register 1 (CiCTLR1 Register) (i = 0, 1)                                  |     |

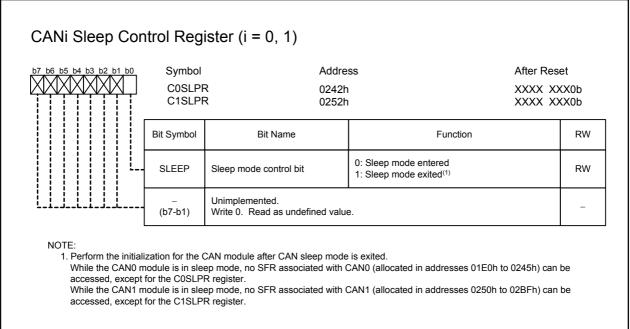

|              | CANi Sleep Control Register (CiSLPR Register) (i = 0, 1)                               |     |

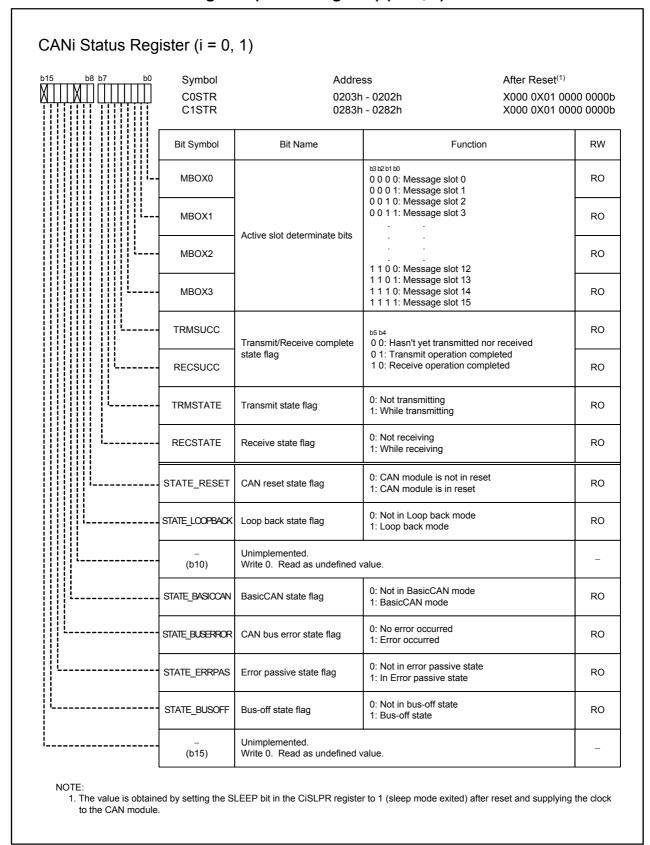

|              | CANi Status Register (CiSTR Register) ( $i = 0, 1$ )                                   |     |

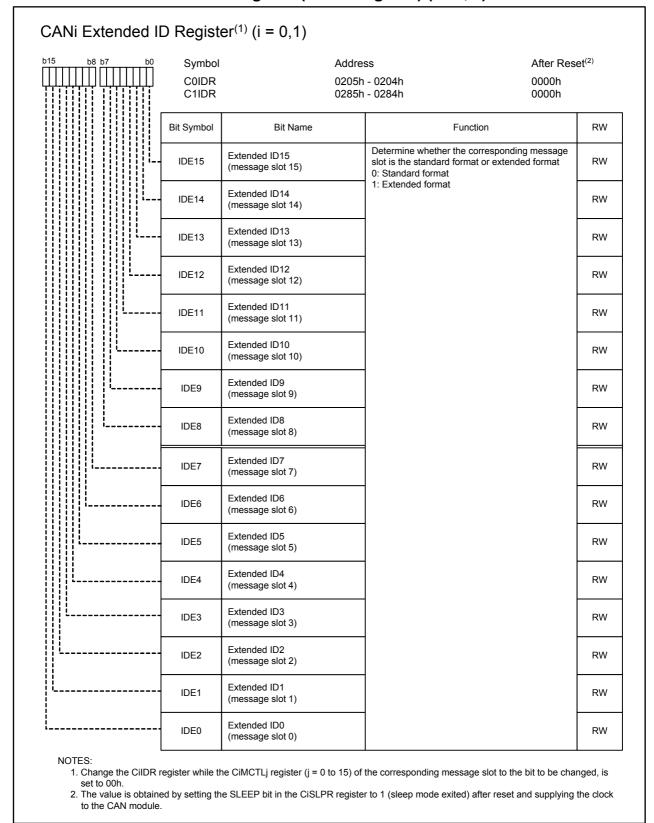

|              | CANi Extended ID Register (CiIDR Register) (i = 0, 1)                                  |     |

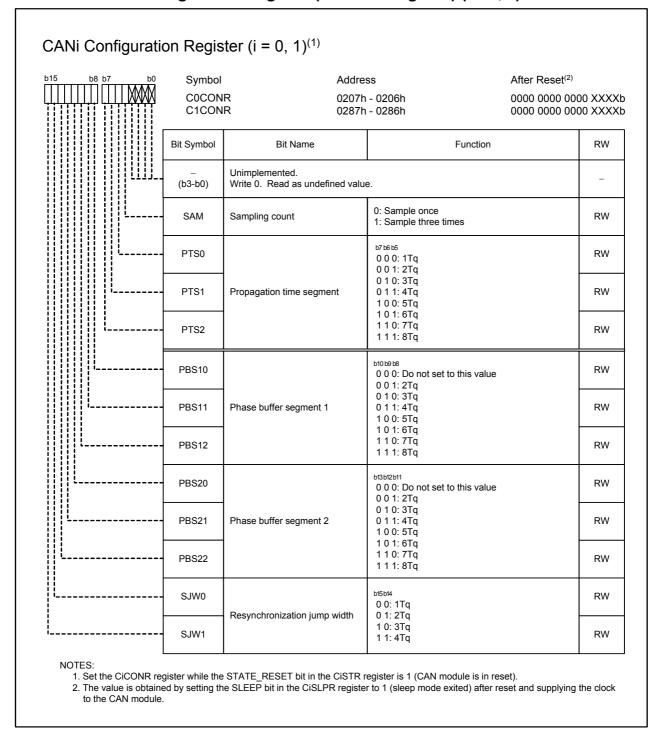

|              | CANi Configuration Register (CiCONR Register) (i = 0, 1)                               |     |

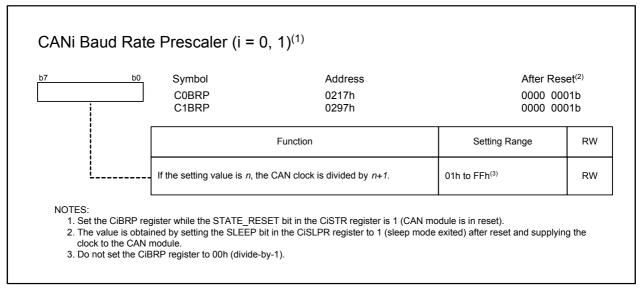

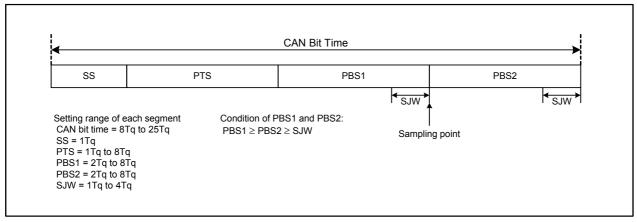

|              | CANi Baud Rate Prescaler (CiBRP Register) (i = 0, 1)                                   |     |

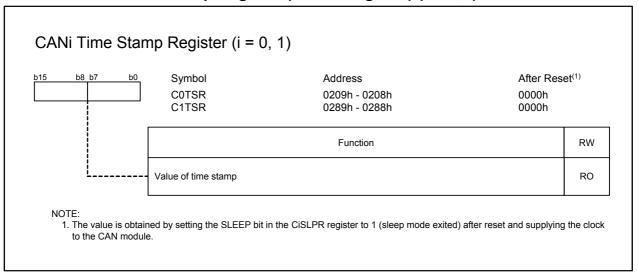

|              | CANi Time Stamp Register (CiTSR Register) (i = 0, 1)                                   |     |

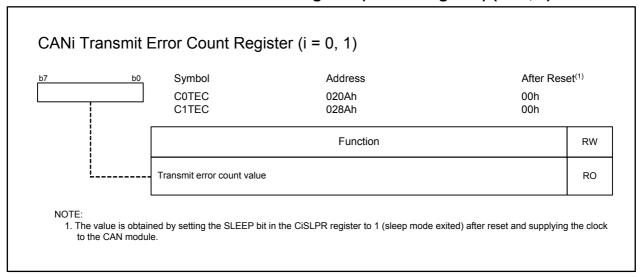

|              | CANi Transmit Error Count Register (CiTEC Register) $(i = 0, 1)$                       |     |

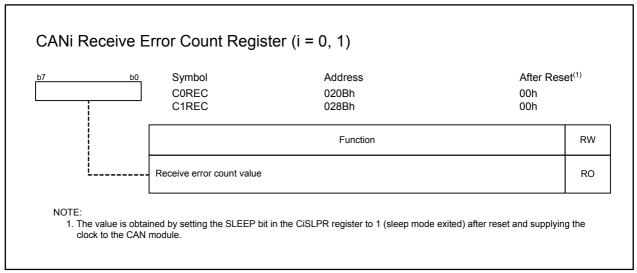

|              | CANi Receive Error Count Register (CiREC Register) (i = 0, 1)                          |     |

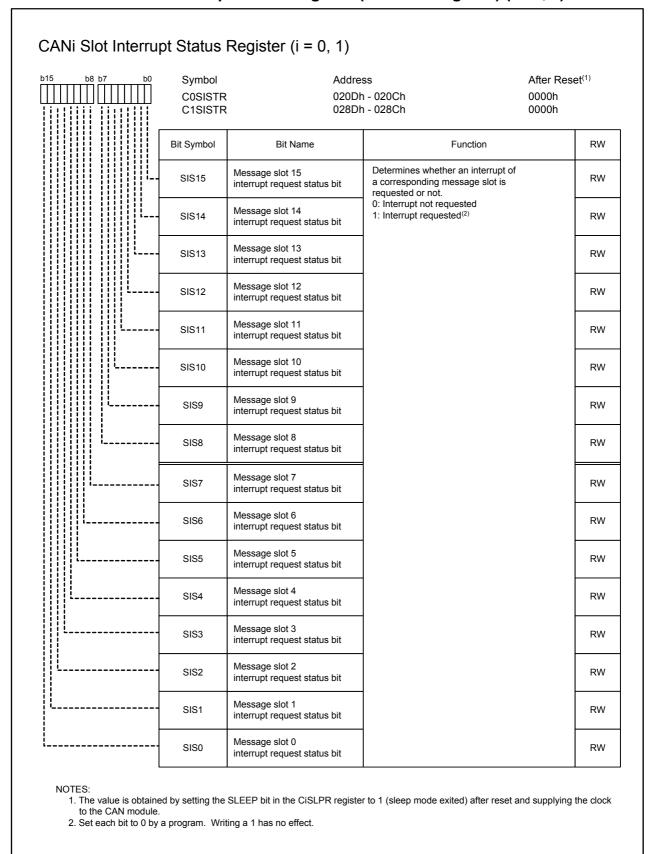

|              | CANi Slot Interrupt Status Register (CiSISTR Register) (i = 0, 1)                      |     |

|              | CANi Slot Interrupt Mask Register (CiSIMKR Register) (i = 0, 1)                        |     |

|              | CANi Error Interrupt Mask Register (CiEIMKR Register) (i = 0, 1)                       |     |

|              | CANi Error Interrupt Status Register (CiEISTR Register) (i = 0, 1)                     |     |

|              | CANi Error Source Register (CiEFR Register) (i = 0, 1)                                 |     |

|              | CANi Mode Register (CiMDR Register) (i = 0, 1)                                         |     |

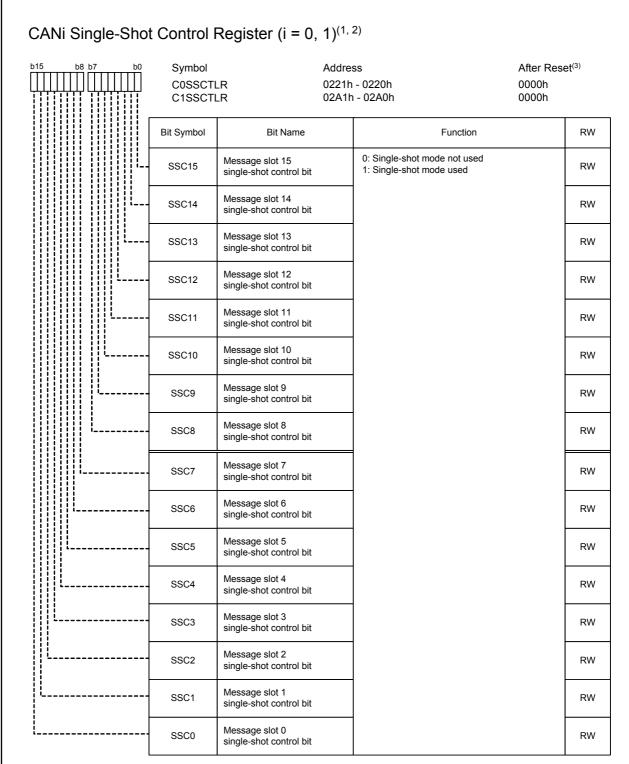

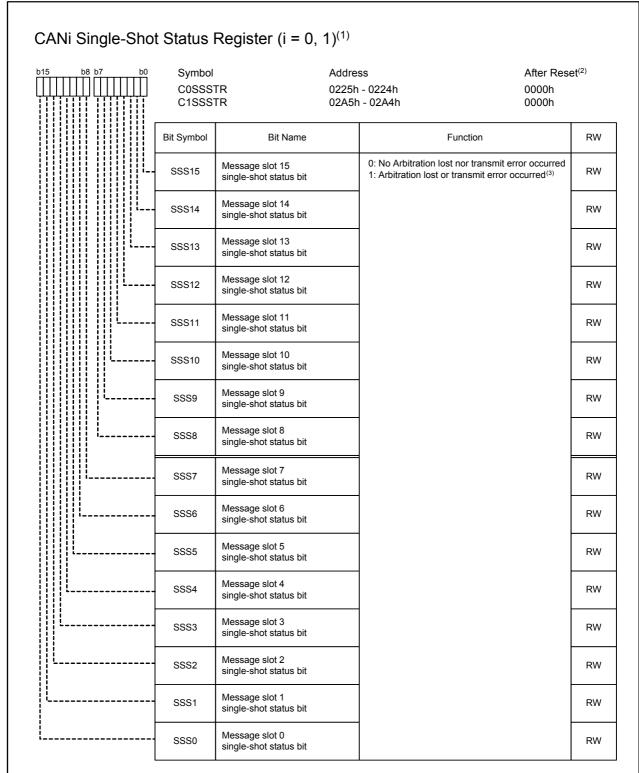

| 23 1 17      | CANi Single-Shot Control Register (CiSSCTLR Register) $(i = 0, 1)$                     | 428 |

| 23.1.1  | 8 CANi Single-Shot Status Register (CiSSSTR Register) (i = 0, 1)                                                                                       | 430   |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

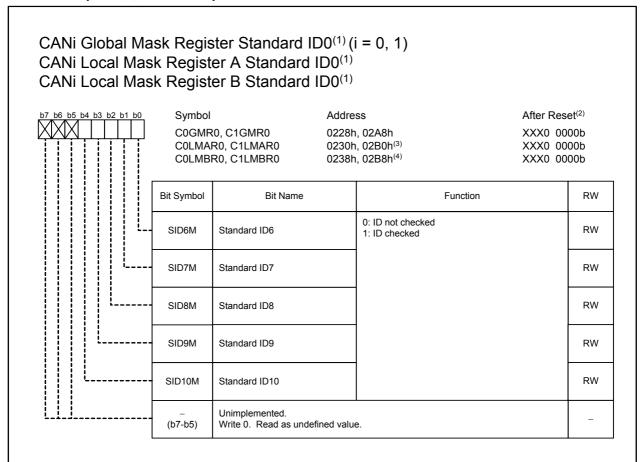

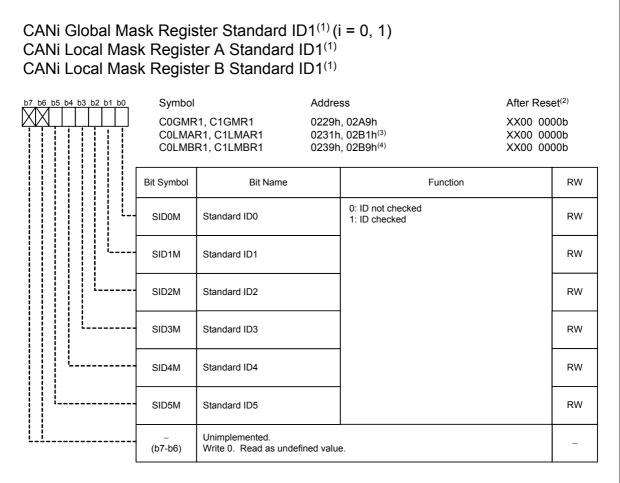

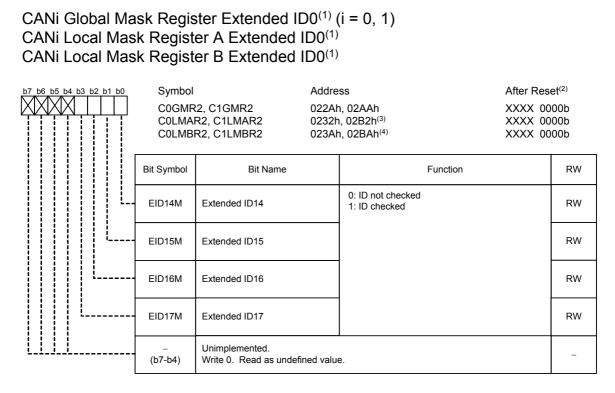

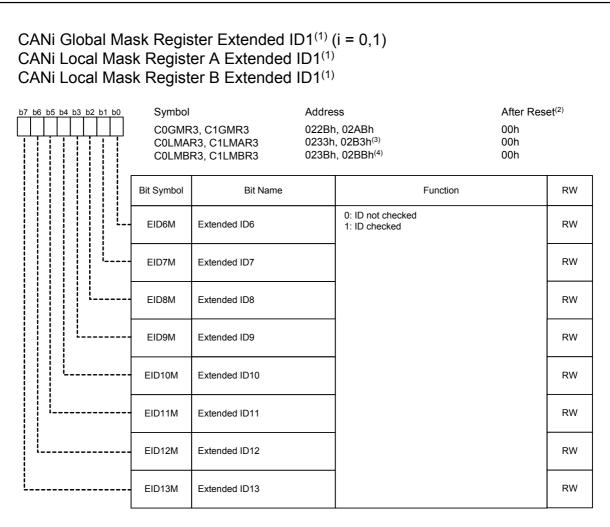

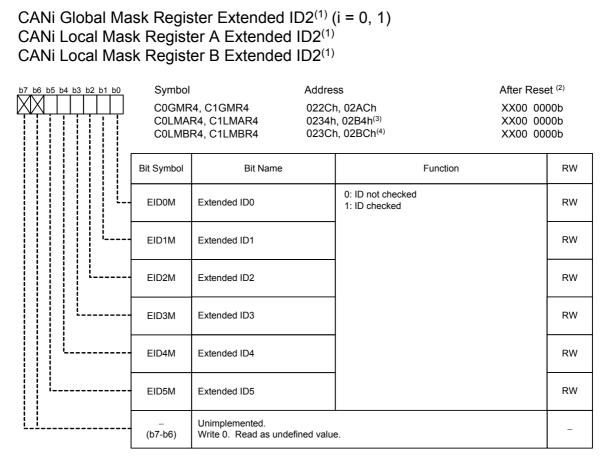

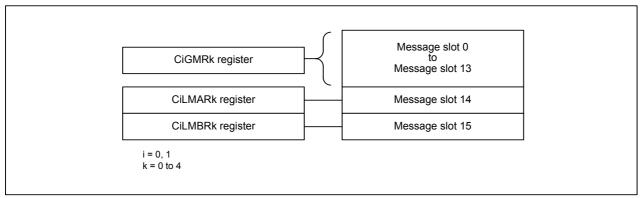

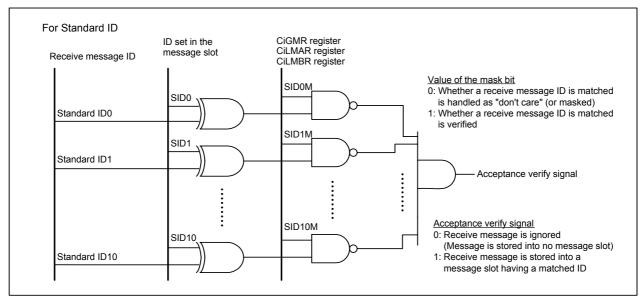

| 23.1.1  | 9 CANi Global Mask Register, CANi Local Mask Register A, and CANi Local Mask Register B (CiGMRk, CiLMARk, and CiLMBRk Registers) (i = 0,1, k = 0 to 4) | 432   |

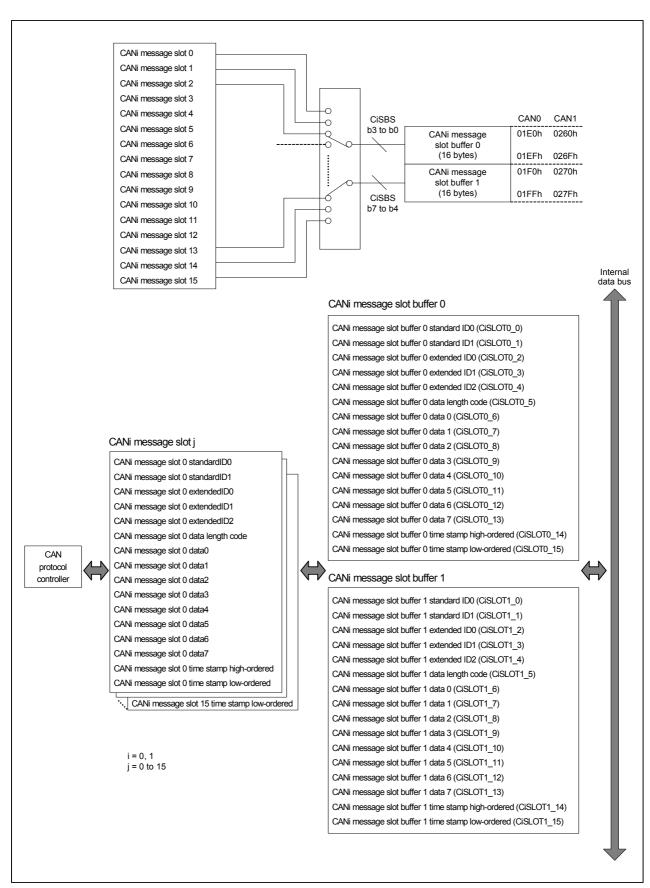

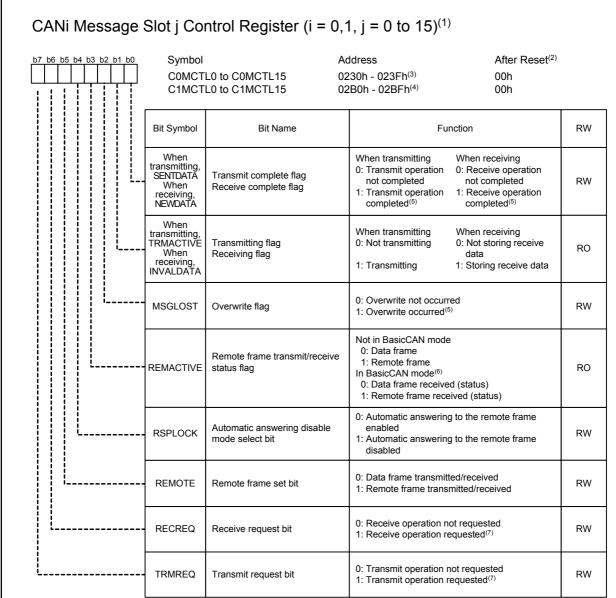

| 23.1.2  | O CANi Message Slot j Control Register (CiMCTLj Register) (i = 0, 1, j = 0 to 15)                                                                      | 438   |

| 23.1.2  | 1 CANi Slot Buffer Select Register (CiSBS Register) (i = 0, 1)                                                                                         | 442   |

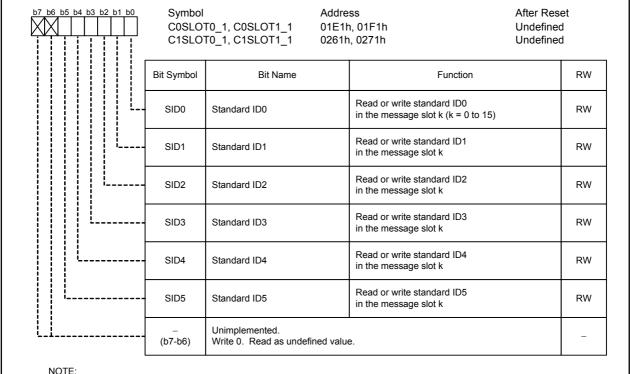

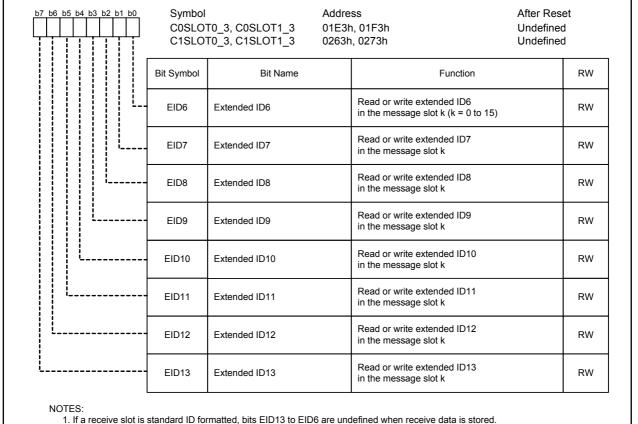

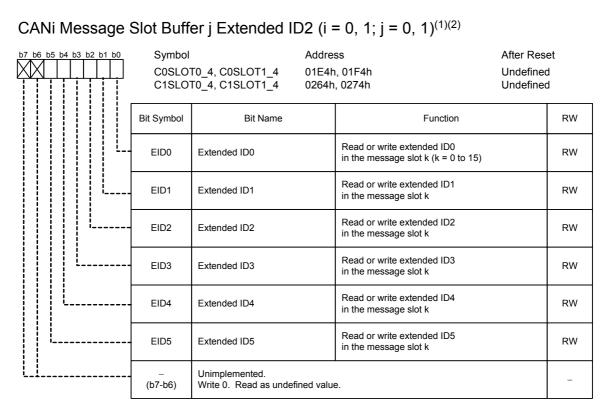

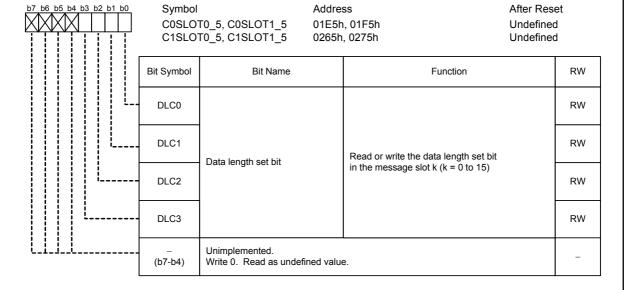

| 23.1.2  | 2 CANi Message Slot Buffer j (i = 0, 1; j = 0, 1)                                                                                                      | 443   |

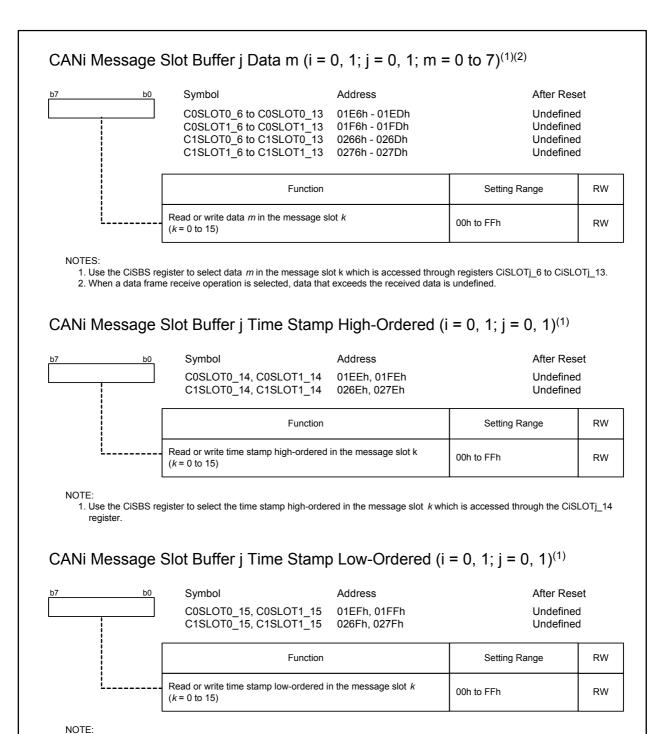

| 23.1.2  | 3 CANi Acceptance Filter Support Register (CiAFS Register) (i = 0, 1)                                                                                  | 447   |

| 23.2    | CAN Clock and CPU Clock                                                                                                                                | 448   |

| 23.2.1  | CAN Clock                                                                                                                                              | 448   |

| 23.2.2  | CPU Clock                                                                                                                                              | 448   |

| 23.3    | Setting and Timing in CAN-Associated Registers                                                                                                         | 449   |

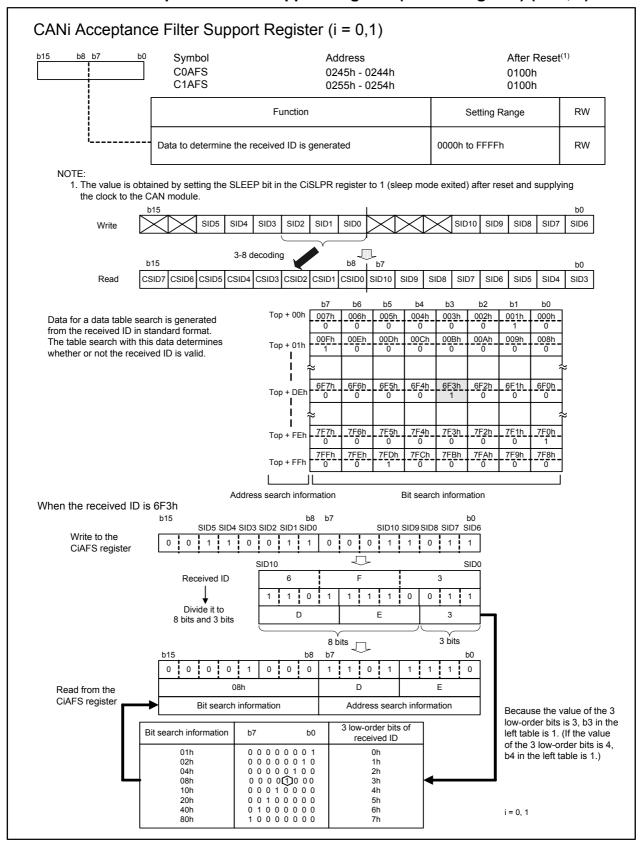

| 23.3.1  | CAN Module Initialize Timing                                                                                                                           | 449   |

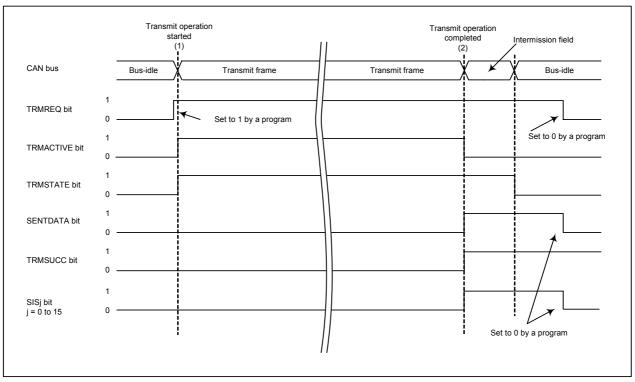

| 23.3.2  | CAN Transmit Timing                                                                                                                                    | 450   |

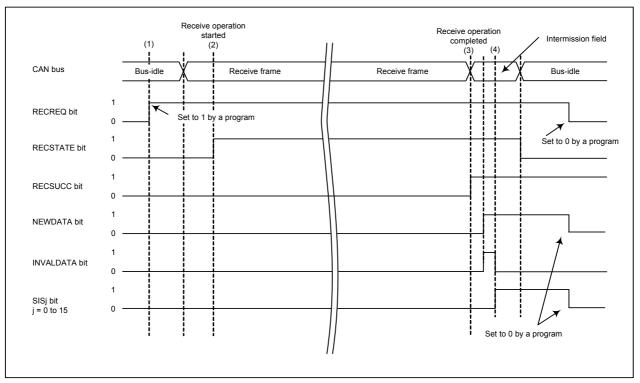

| 23.3.3  | CAN Receive Timing                                                                                                                                     | 451   |

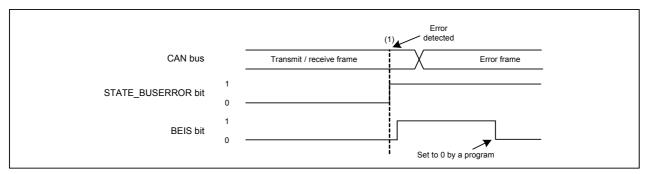

| 23.3.4  | CAN Bus Error Timing                                                                                                                                   | 452   |

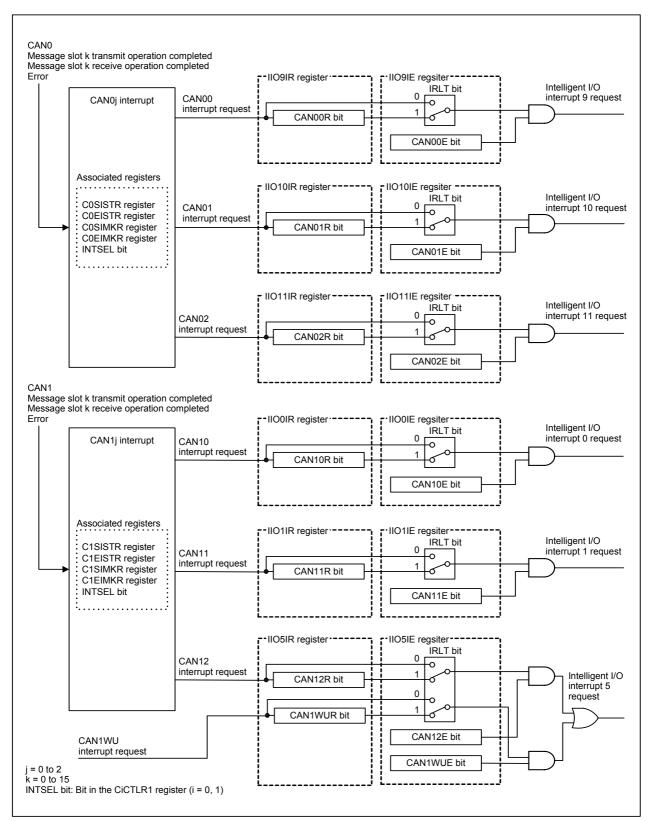

| 23.4    | CAN Interrupts                                                                                                                                         | 453   |

| 23.4.1  | CAN1 Wake-Up Interrupt                                                                                                                                 | 454   |

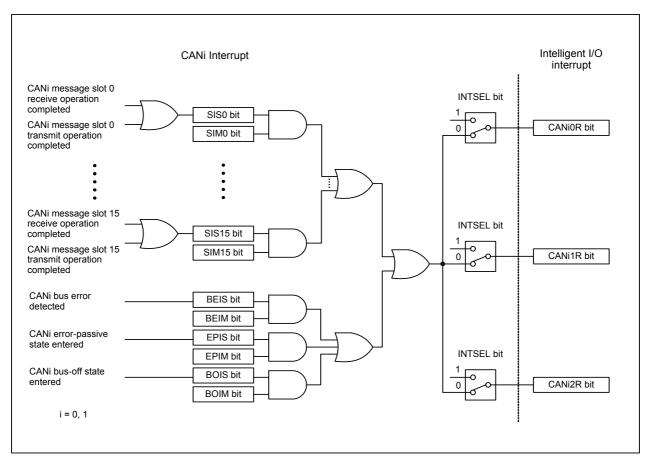

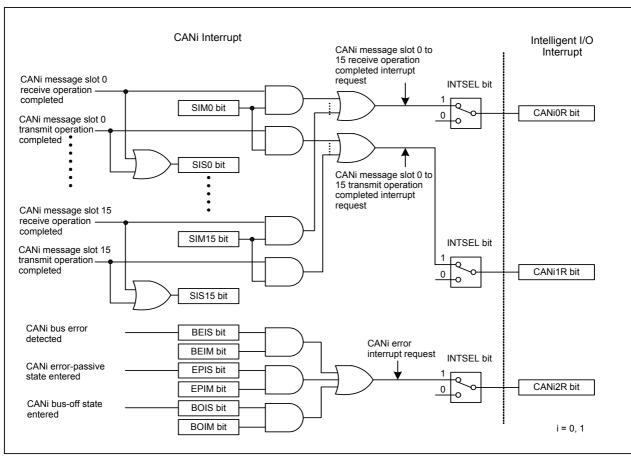

| 23.4.2  | CANij Interrupt                                                                                                                                        | 454   |

| 24. Re  | al-Time Port (RTP)                                                                                                                                     | . 458 |

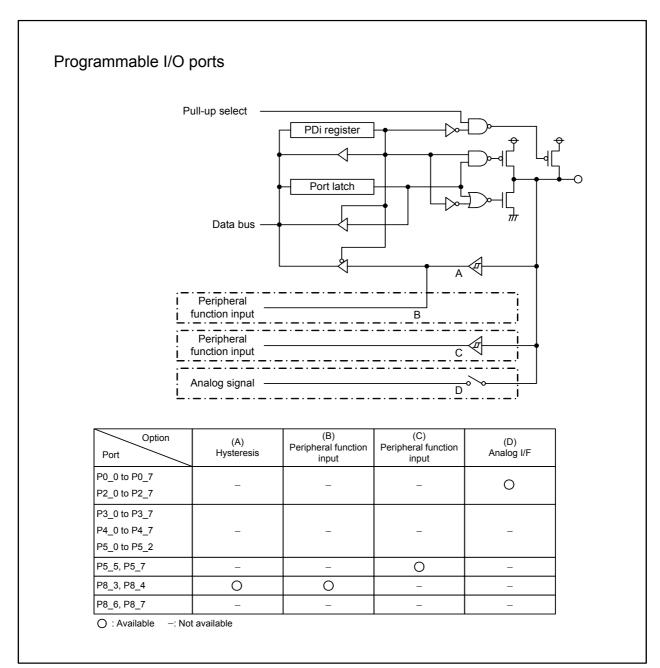

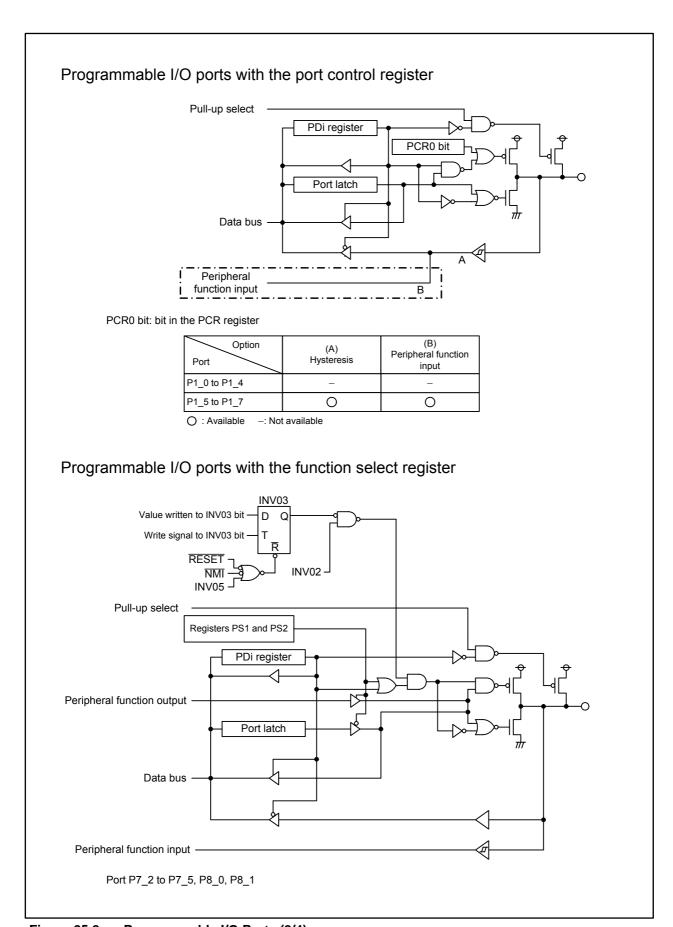

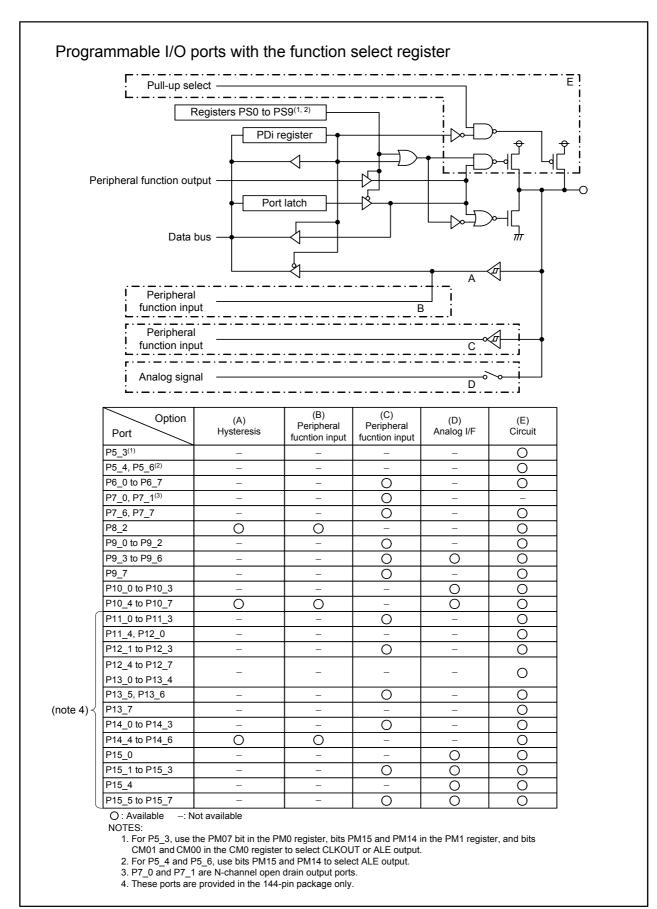

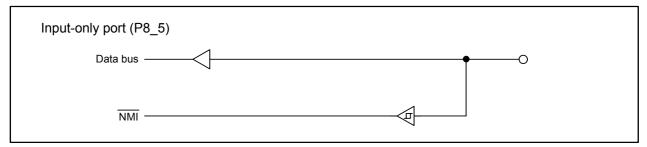

| 25. Pro | grammable I/O Ports                                                                                                                                    | . 461 |

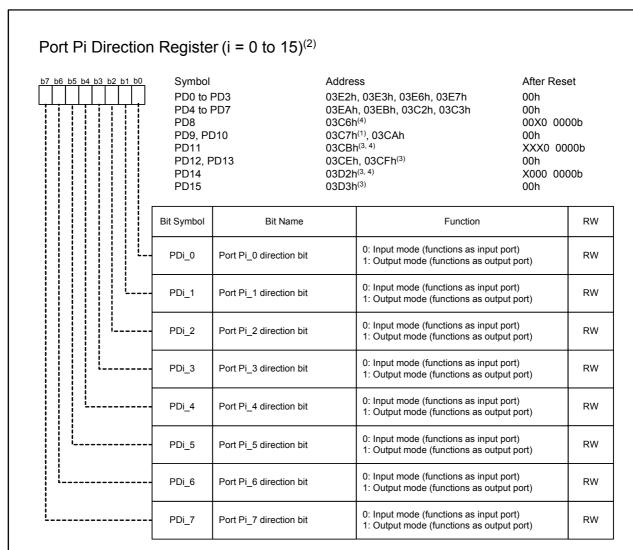

| 25.1    | Port Pi Direction Register (PDi Register, i = 0 to 15)                                                                                                 | 461   |

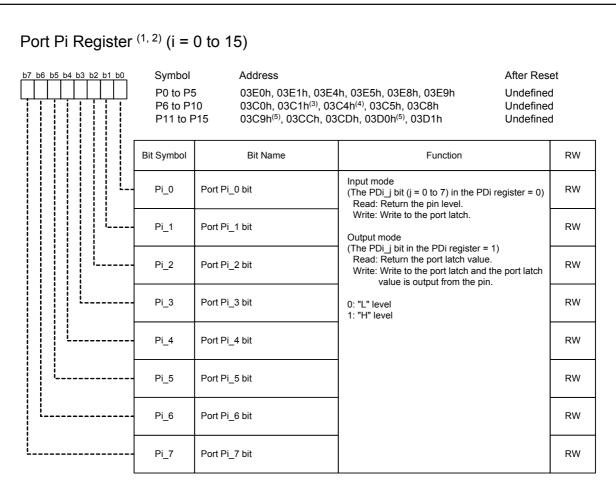

| 25.2    | Port Pi Register (Pi Register, i = 0 to 15)                                                                                                            |       |

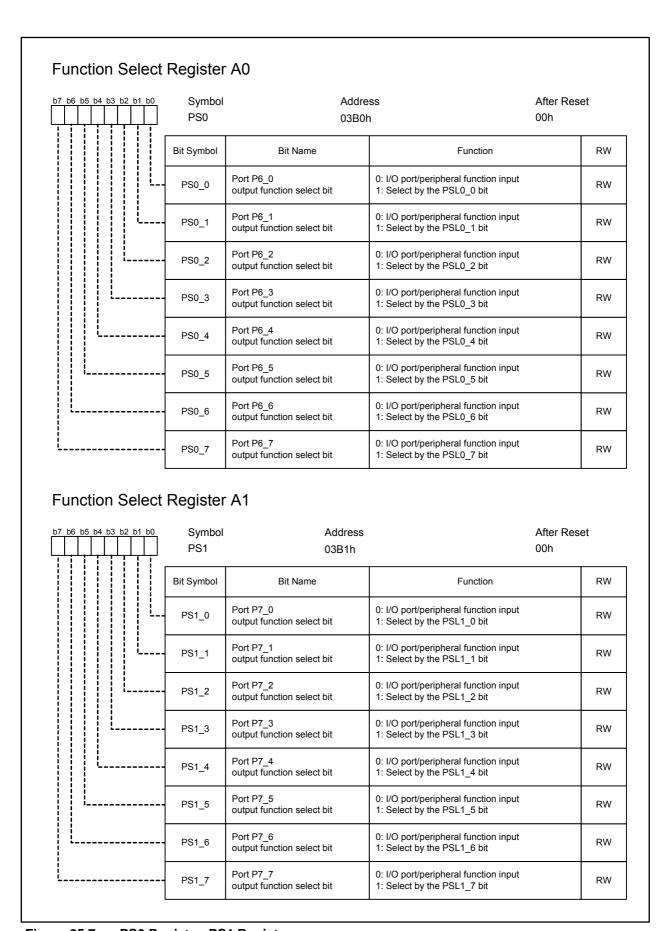

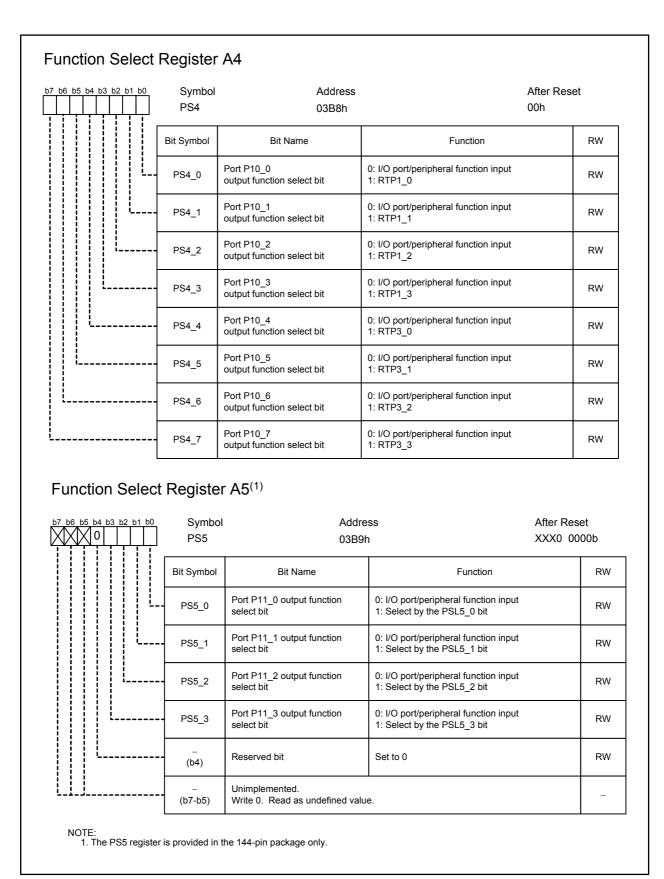

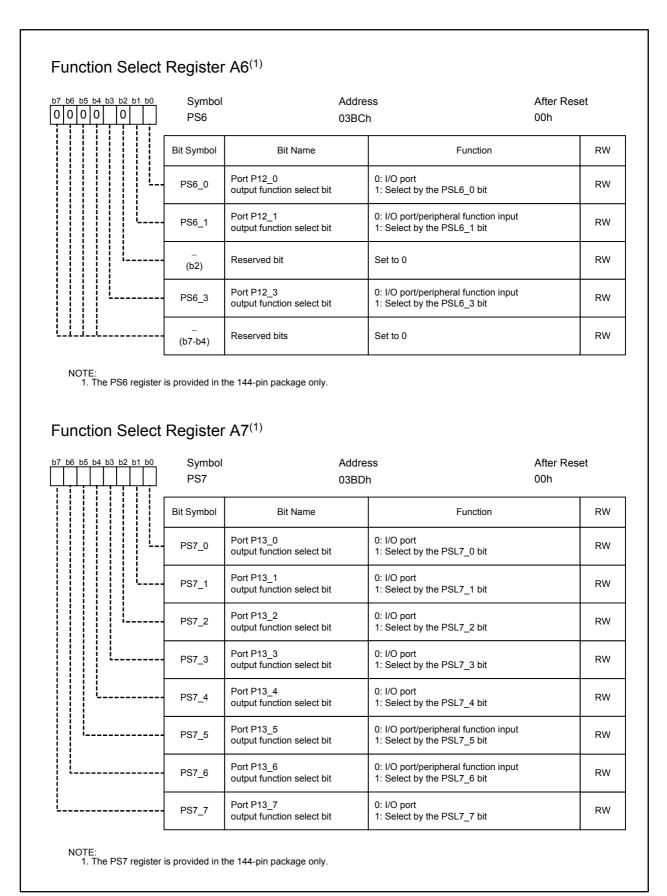

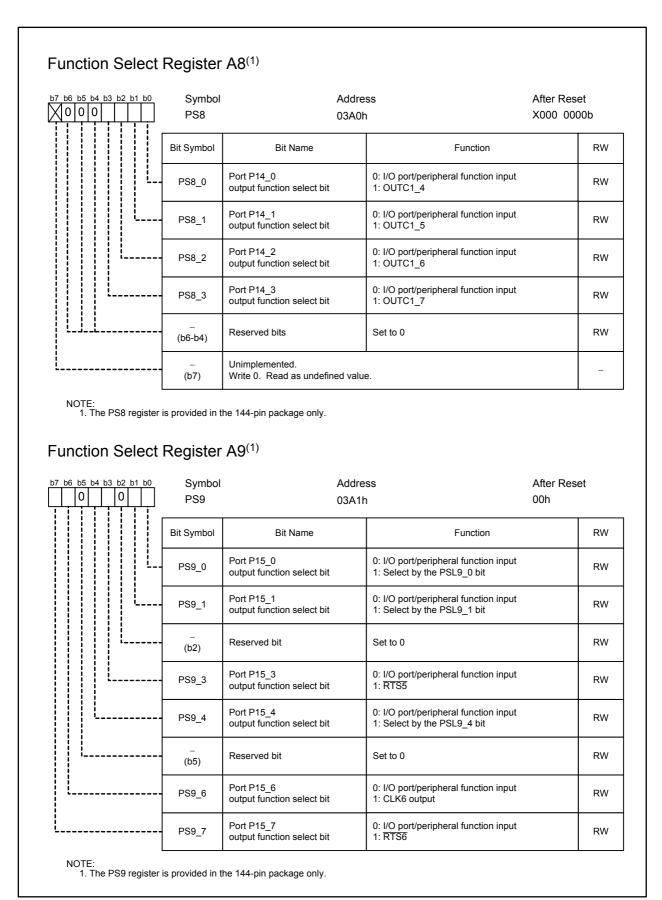

| 25.3    | Function Select Register A (PSj Register, j = 0 to 9)                                                                                                  |       |

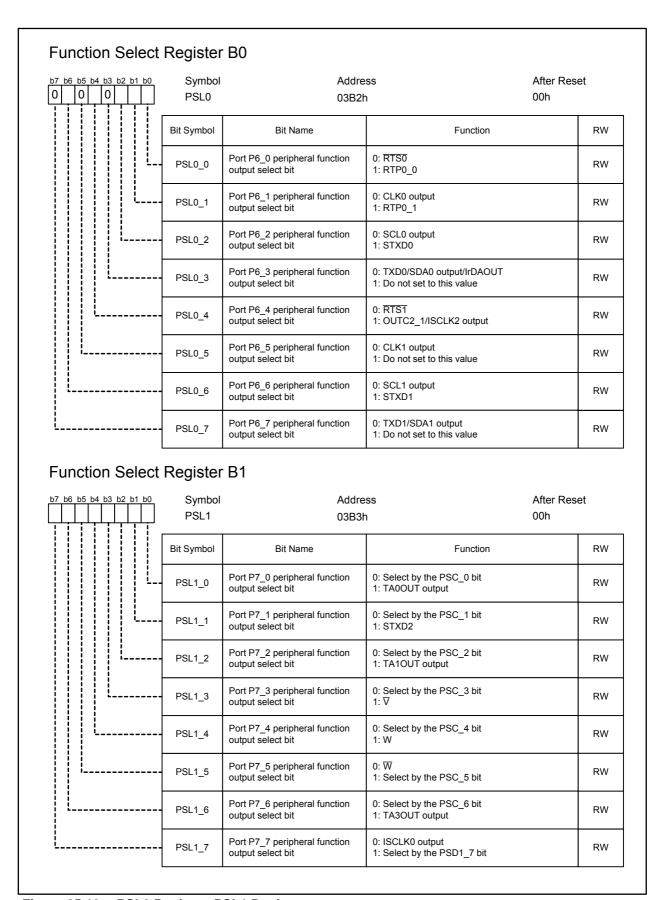

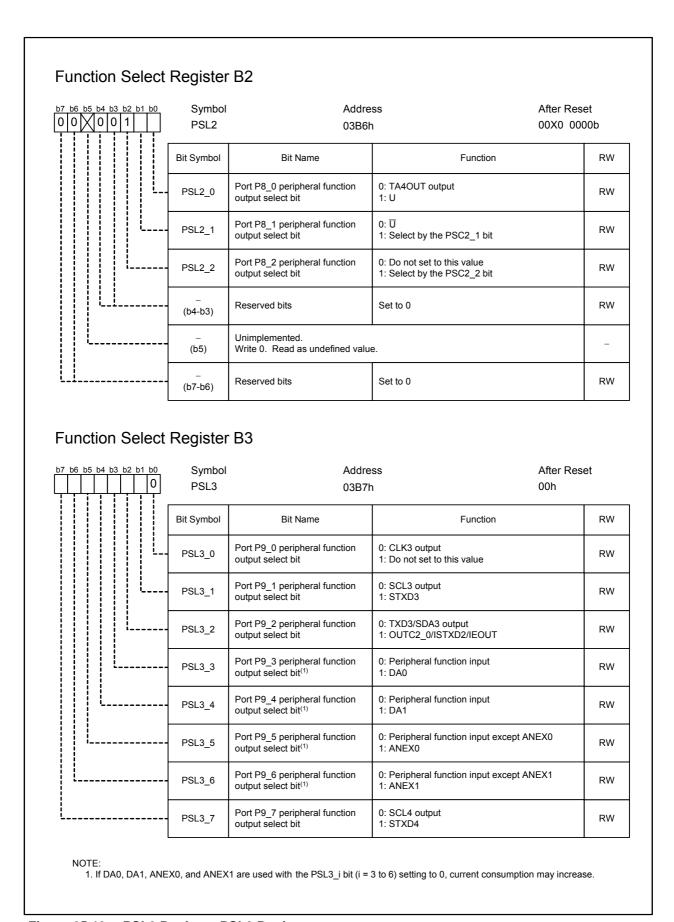

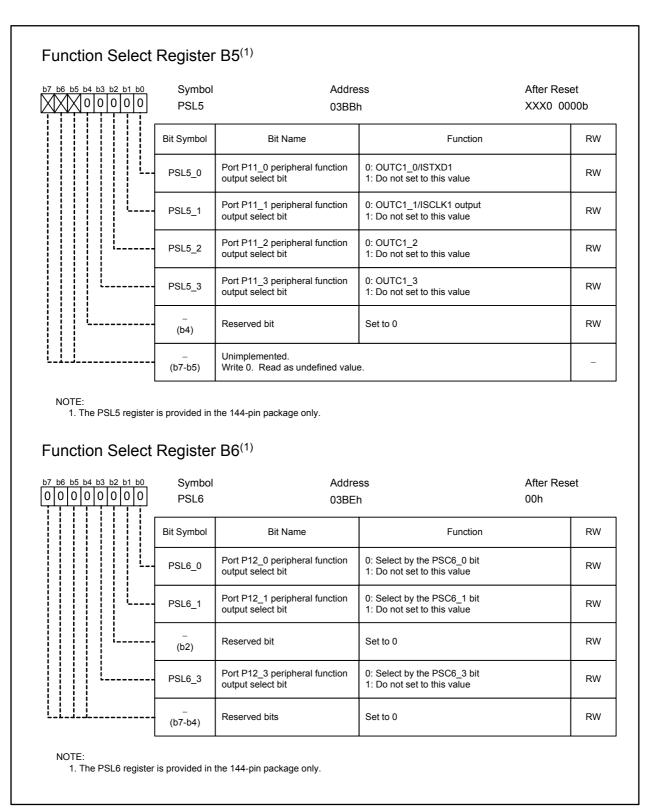

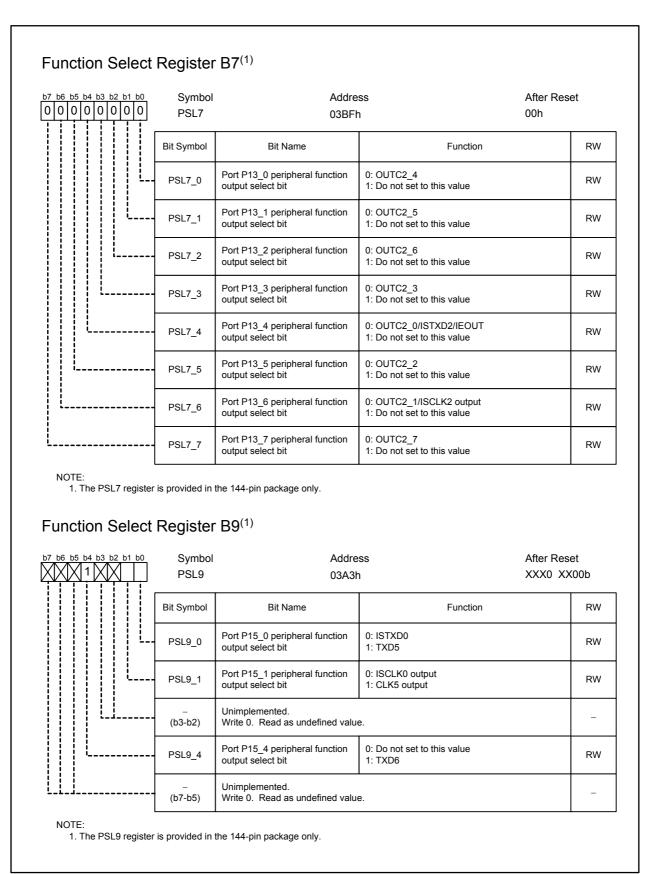

| 25.4    | Function Select Register B (PSLk Register, k = 0 to 3, 5 to 7, 9)                                                                                      |       |

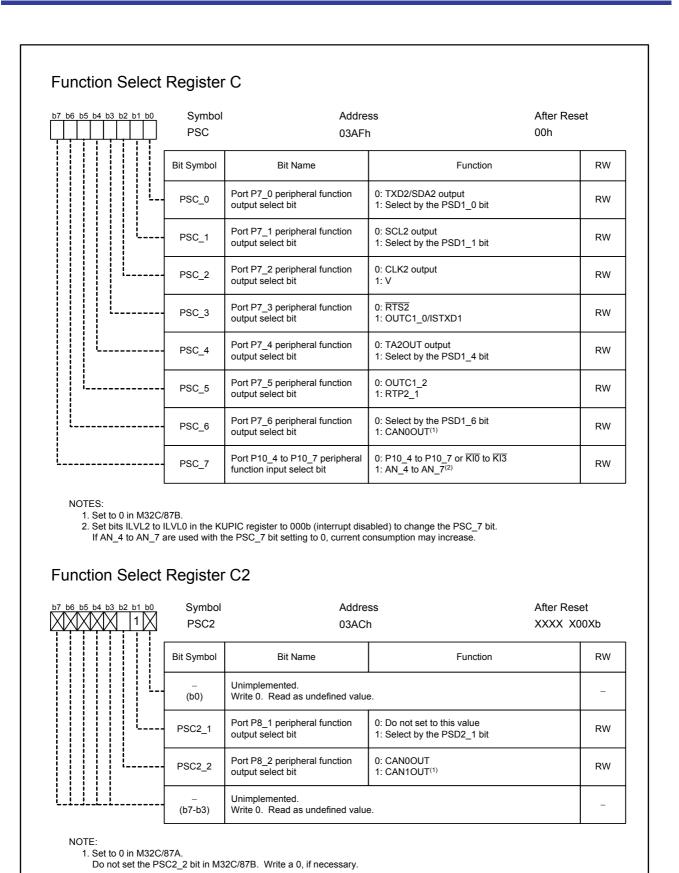

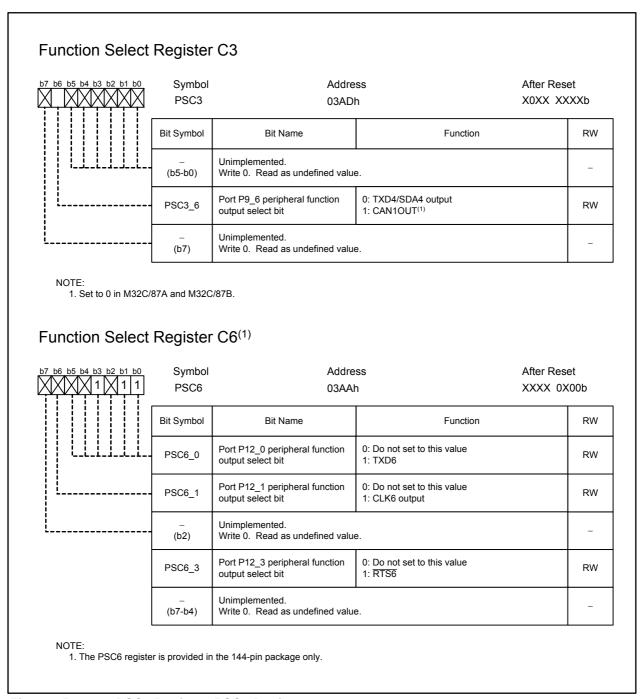

| 25.5    | Function Select Register C (PSC, PSC2, PSC3, and PSC6 Registers)                                                                                       |       |

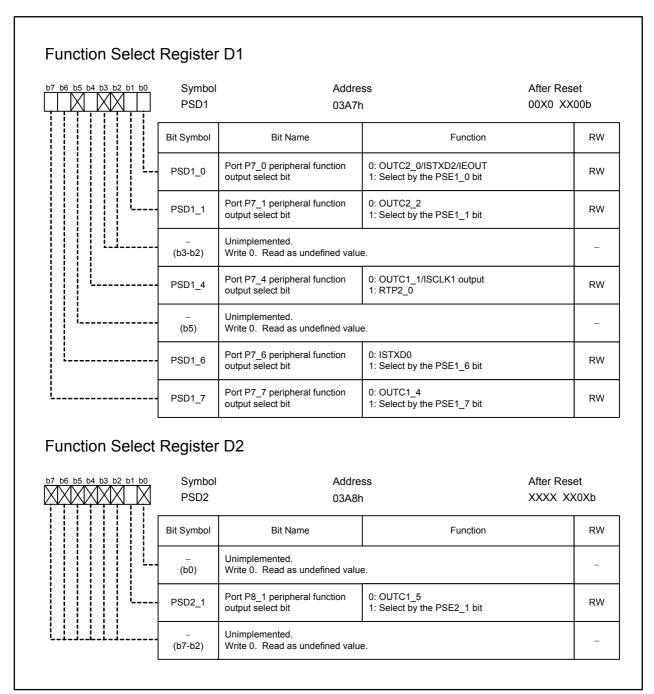

| 25.6    | Function Select Register D (PSD1 and PSD2 Registers)                                                                                                   |       |

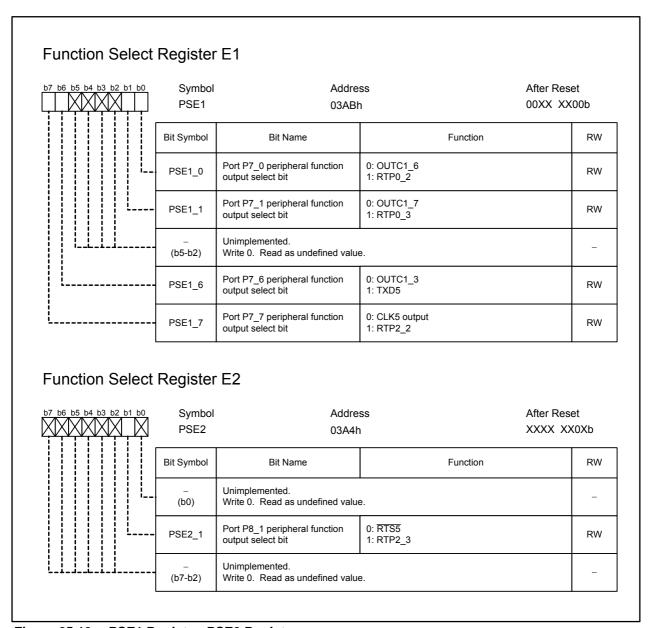

| 25.7    | Function Select Register E (PSE1 and PSE2 Registers)                                                                                                   | 462   |

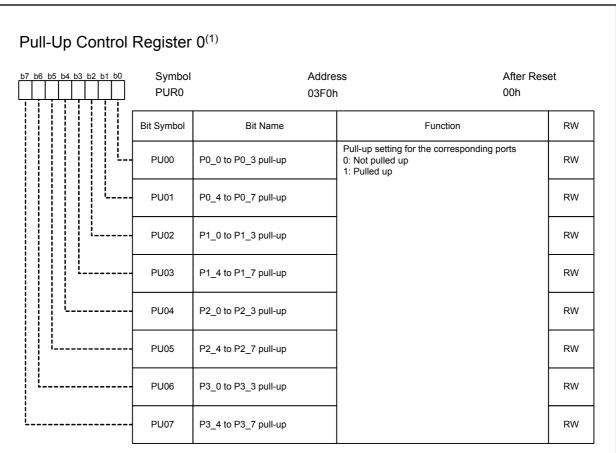

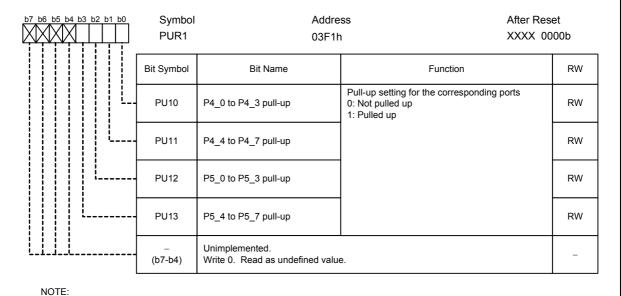

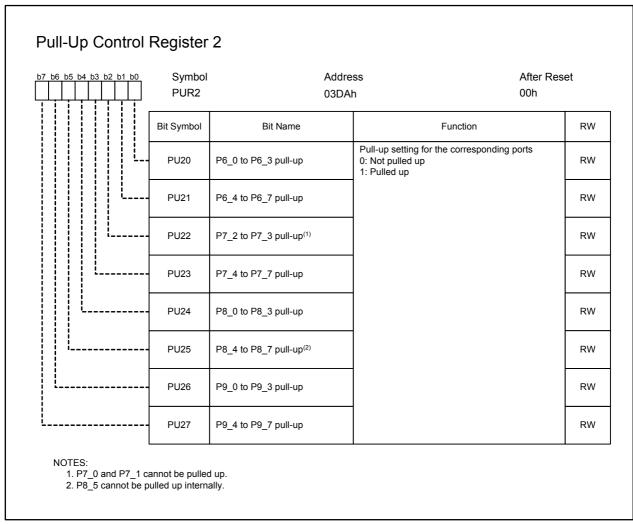

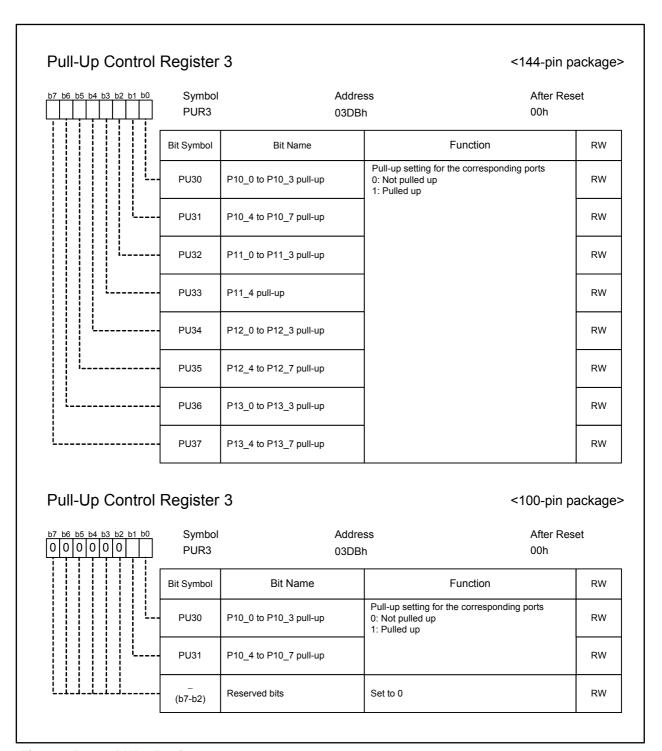

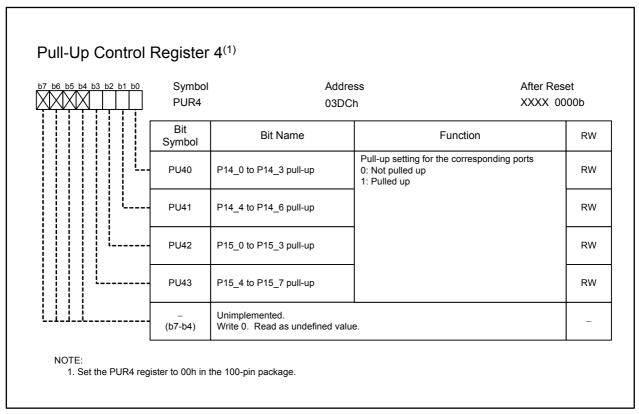

| 25.8    | Pull-up Control Register 0 to 4 (PUR0 to PUR4 Registers)                                                                                               |       |

| 25.9    | Port Control Register (PCR Register)                                                                                                                   |       |

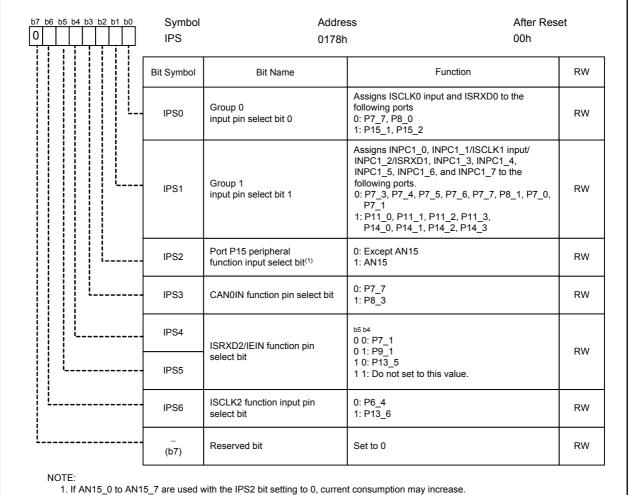

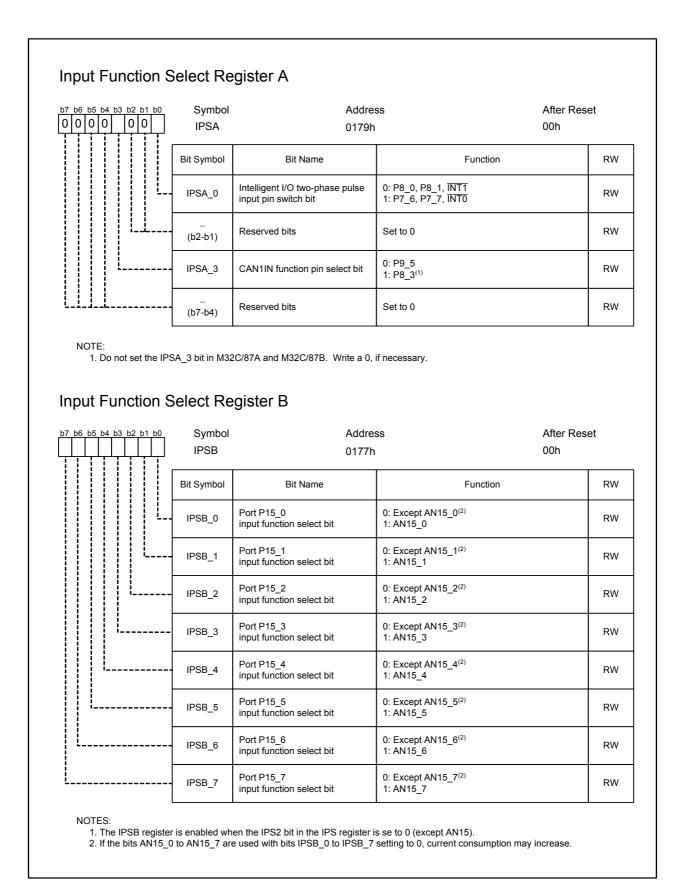

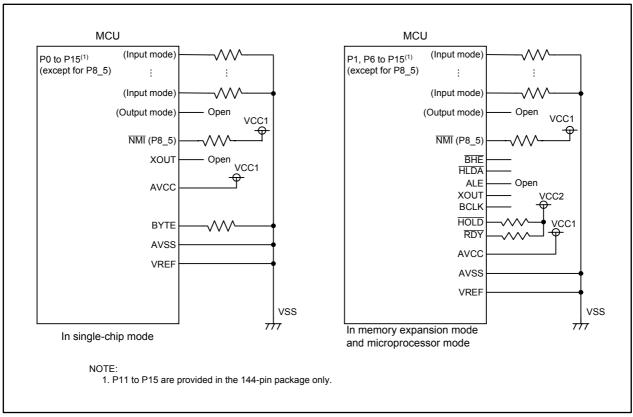

| 25.10   | Input Function Select Register (IPS, IPSA, and IPSB Registers)                                                                                         | 462   |

| 25.11   | Analog Input and Other Peripheral Function Input                                                                                                       | 462   |

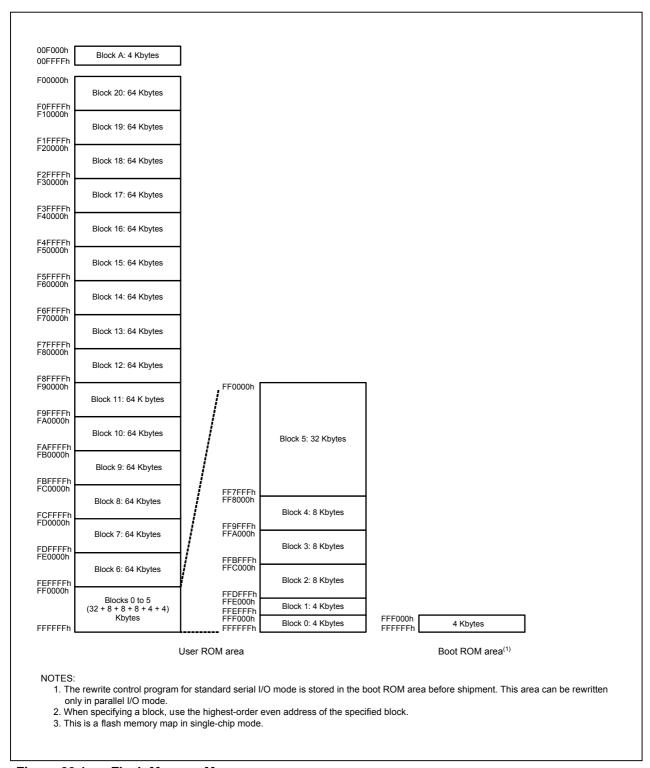

| 26. Fla | sh Memory                                                                                                                                              | . 493 |

| 26.1    | Memory Map                                                                                                                                             |       |

| 26.1.1  | • •                                                                                                                                                    |       |

| 26.2    | Functions to Prevent Access to Flash Memory                                                                                                            |       |

| 26.2.1  | •                                                                                                                                                      |       |

| 26.2.2  |                                                                                                                                                        |       |

| 26.3    | CPU Rewrite Mode                                                                                                                                       |       |

| 26.3.1  | Flash Memory Control Register (FMR0 and FMR1 Registers)                                                                                                |       |

| 26.3.2  |                                                                                                                                                        |       |

| 26.3.3  |                                                                                                                                                        |       |

| 26.3.4  |                                                                                                                                                        |       |

| 26.3.5  |                                                                                                                                                        |       |

| 26.4    | Standard Serial I/O Mode                                                                                                                               |       |

| 26.4.1  |                                                                                                                                                        |       |

| 26.5    | Parallel I/O Mode                                                                                                                                      |       |

|         | Boot ROM Area                                                                                                                                          |       |

| 27.          | Electrical Characteristics                   | 519   |

|--------------|----------------------------------------------|-------|

| 28.          | Usage Notes                                  | 556   |

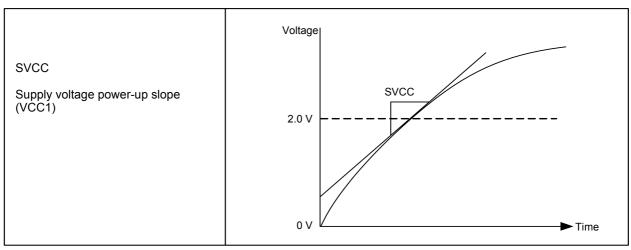

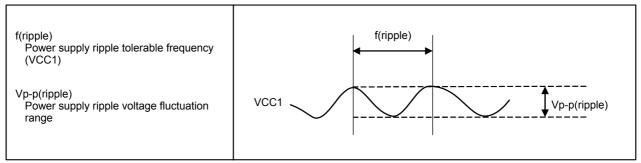

| 28.1         | Power Supply                                 | . 556 |

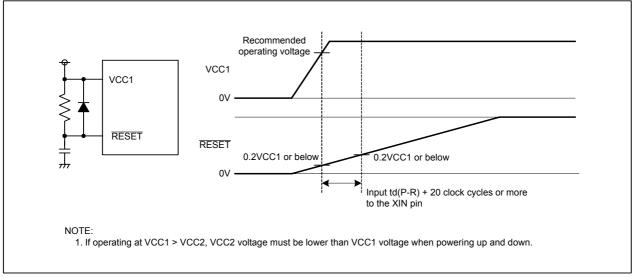

| 28           | .1.1 Power-on                                |       |

| 28           | .1.2 Power Supply Ripple                     |       |

| 28           | .1.3 Noise                                   |       |

| 28.2         |                                              |       |

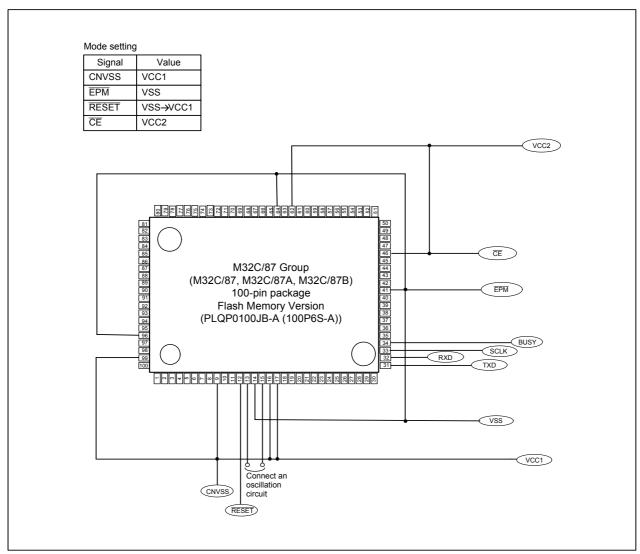

|              | .2.1 100 Pin-Package                         |       |

| _            | .2.2 Register Settings                       |       |

| 28.3         |                                              |       |

| 28.4         |                                              |       |

| _            | .4.1 HOLD Input                              |       |

| 28.5         |                                              |       |

|              | .5.1 Main Clock                              |       |

| _            | .5.2 Sub Clock                               |       |

| _            | .5.3 Clock Dividing Ratio                    |       |

|              | .5.4 Power Consumption Control               |       |

| 28.6<br>28.7 |                                              |       |

|              | Interrupts                                   |       |

|              | 7.2 NMI Interrupt                            |       |

| _            | .7.3 INT Interrupt                           |       |

|              | 7.4 Changing Interrupt Control Register      |       |

|              | 7.5 Changing IIOiIR Register (i = 0 to 11)   |       |

|              | .7.6 Changing RLVL Register                  |       |

| 28.8         |                                              |       |

| 28.9         |                                              |       |

|              | .9.1 Timer A, Timer B                        |       |

|              | 9.2 Timer A                                  |       |

| _            | 9.3 Timer B                                  |       |

| 28.10        |                                              |       |

| 28.1         |                                              |       |

| 28           | .11.1 Changing UiBRG Register (i = 0 to 6)   |       |

|              | .11.2 Clock Synchronous Mode                 |       |

| 28           | .11.3 UART Mode                              |       |

|              | .11.4 Special Mode 1 (I <sup>2</sup> C Mode) |       |

| 28.12        |                                              |       |

| 28.13        | 3 Intelligent I/O                            | . 576 |

| 28           | .13.1 Register Setting                       | . 576 |

| 28.14        | 4 CAN                                        | . 577 |

| 28.13        | 5 Programmable I/O Ports                     | . 578 |

| 28.10        | 6 Flash Memory                               | . 579 |

| 28           | .16.1 Operating Speed                        | . 579 |

| 28           | .16.2 Prohibited Instructions                | . 579 |

| 28           | .16.3 Interrupts (EW0 Mode)                  | . 579 |

| 28           | .16.4 Interrupts (EW1 Mode)                  | . 579 |

| 28           | .16.5 How to Access                          | . 579 |

| 28           | .16.6 Rewriting User ROM Area (EW0 Mode)     | . 579 |

| 28           | .16.7 Rewriting User ROM Area (EW1 Mode)     | . 579 |

|            | Boot Mode                                                                    |     |

|------------|------------------------------------------------------------------------------|-----|

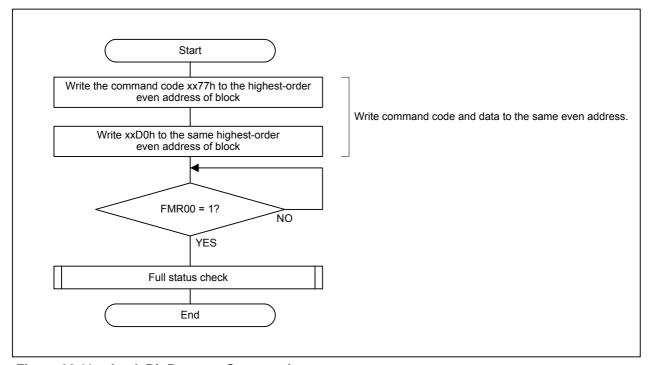

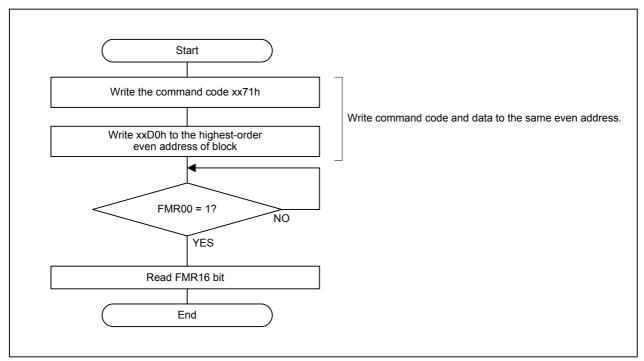

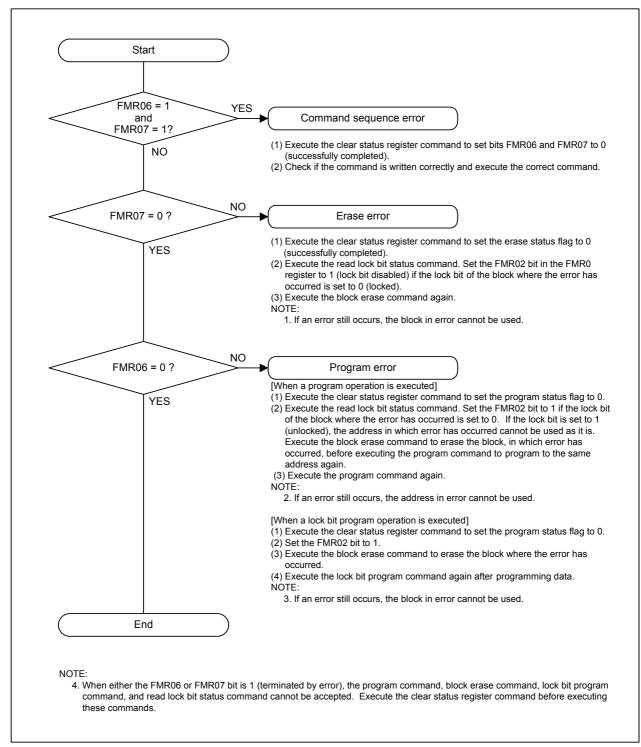

| 28.16.9    | Writing Command and Data                                                     | 580 |

| 28.16.10   | Block Erase                                                                  | 580 |

| 28.16.11   | Wait Mode                                                                    | 580 |

| 28.16.12   | 2 Stop Mode                                                                  | 580 |

| 28.16.13   | Low-Power Consumption Mode and On-Chip Oscillator Low-Power Consumption Mode | 580 |

| 28.17 D    | Difference Between Flash Memory Version and Mask ROM Version                 | 581 |

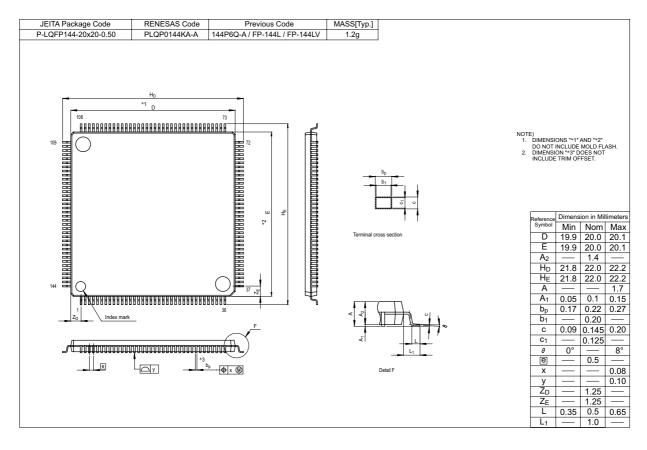

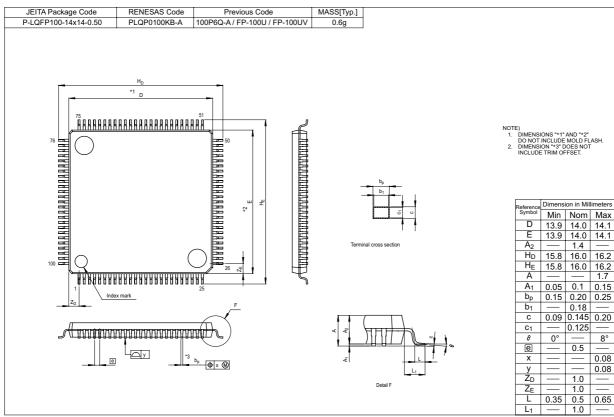

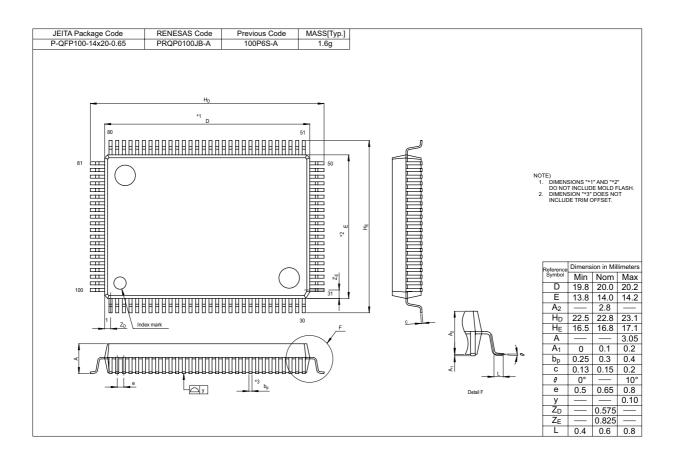

| Appendix 1 | . Package Dimensions                                                         | 582 |

| Index      |                                                                              | 584 |

| Address                                                                                         | Register                                                                      | Symbol         | Page     |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------|----------|

| 0000h                                                                                           | Ŭ                                                                             |                | Ĭ        |

| 0001h                                                                                           |                                                                               |                |          |

| 0002h                                                                                           |                                                                               |                |          |

| 0003h                                                                                           |                                                                               |                |          |

| 0004h                                                                                           | Processor Mode Register 0                                                     | PM0            | 60       |

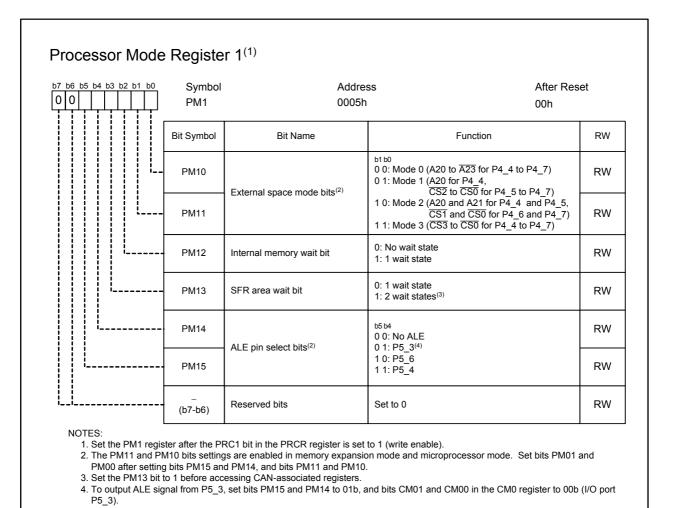

| 0005h                                                                                           | Processor Mode Register 1                                                     | PM1            | 61       |

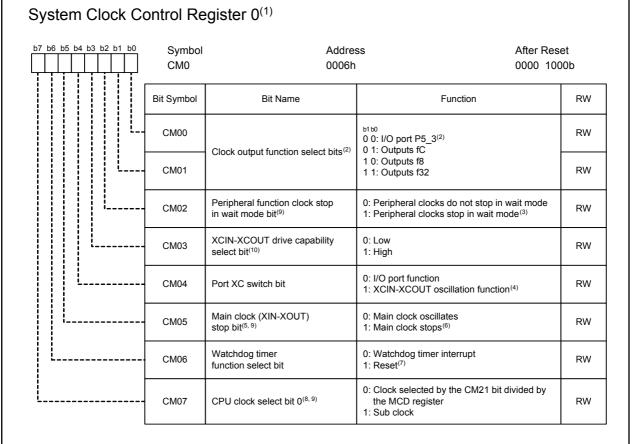

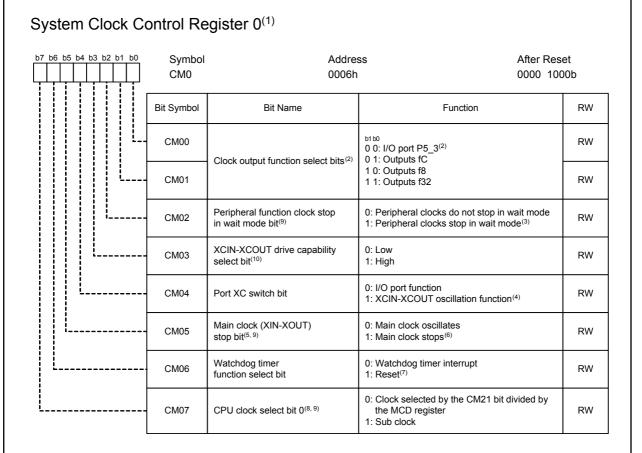

| 0006h                                                                                           | System Clock Control Register 0                                               | CM0            | 82, 136  |

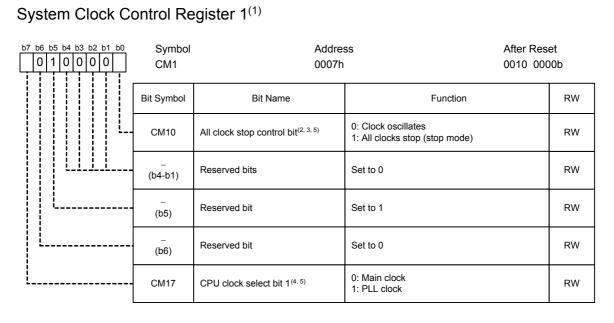

| 0007h                                                                                           | System Clock Control Register 1                                               | CM1            | 83       |

| 0008h                                                                                           |                                                                               |                |          |

| 0009h                                                                                           | Address Match Interrupt Enable Register                                       | AIER           | 127      |

| 000Ah                                                                                           | Protect Register                                                              | PRCR           | 105      |

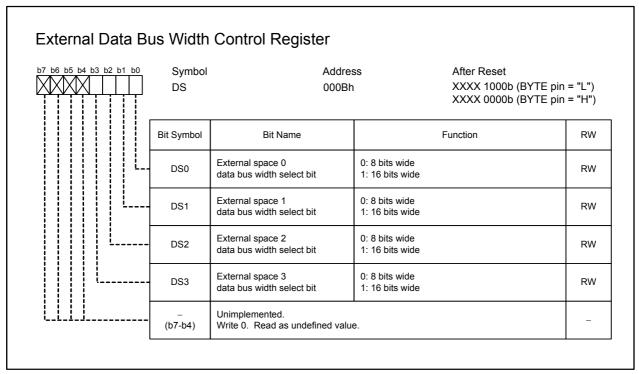

| 000Bh                                                                                           | External Data Bus Width Control Register                                      | DS             | 63       |

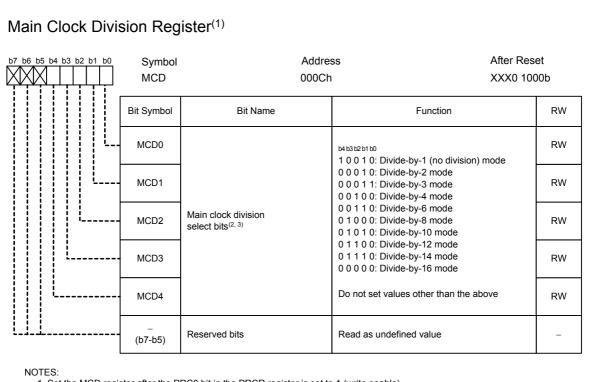

| 000Ch                                                                                           | Main Clock Division Register                                                  | MCD            | 84       |

| 000Dh                                                                                           | Oscillation Stop Detection Register                                           | CM2            | 85       |

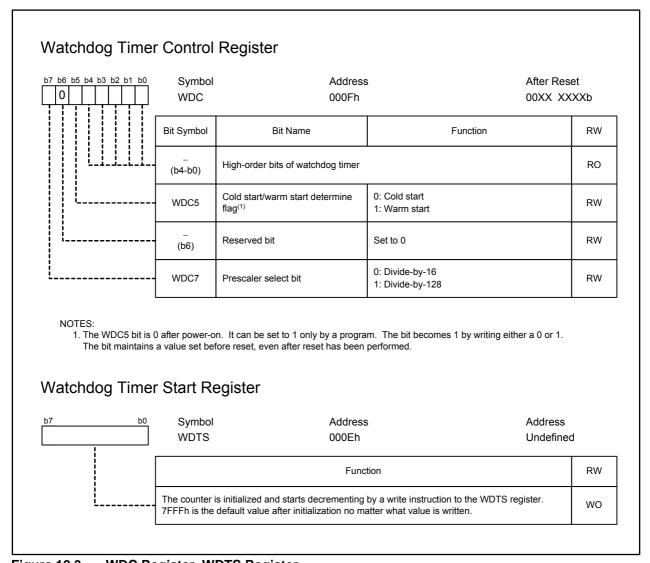

| 000Eh                                                                                           | Watchdog Timer Start Register                                                 | WDTS           | 137      |

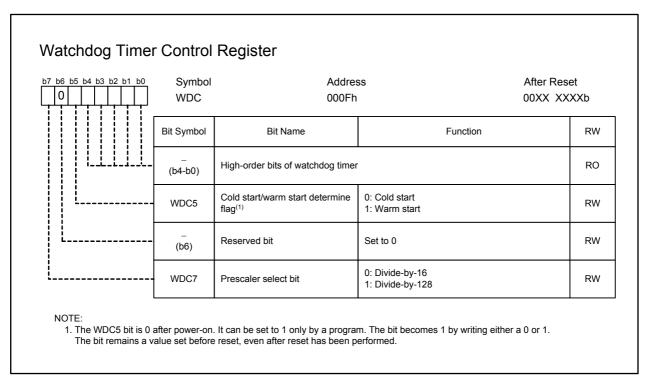

| 000Fh                                                                                           | Watchdog Timer Control Register                                               | WDC            | 54, 137  |

| 0010h                                                                                           |                                                                               |                |          |

| 0011h                                                                                           | Address Match Interrupt Register 0                                            | RMAD0          | 127      |

| 0012h                                                                                           |                                                                               |                |          |

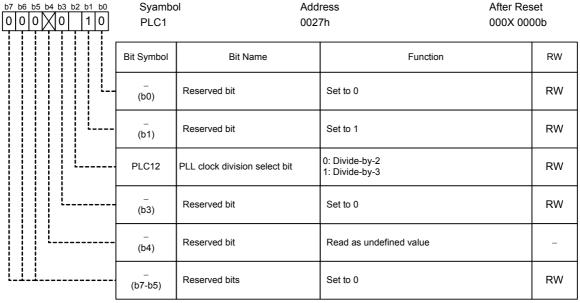

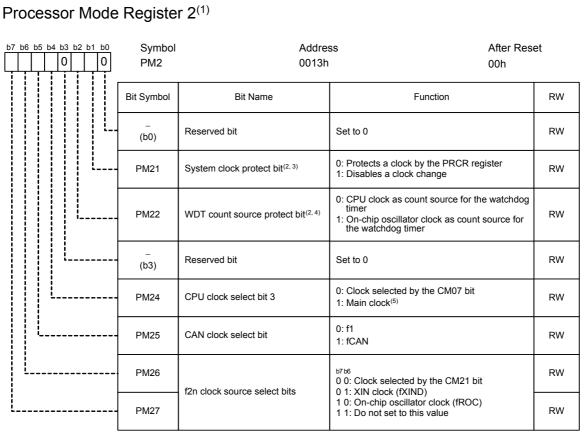

| 0013h                                                                                           | Processor Mode Register 2                                                     | PM2            | 87       |

| 0014h                                                                                           |                                                                               |                |          |

| 0015h                                                                                           | Address Match Interrupt Register 1                                            | RMAD1          | 127      |

| 0016h                                                                                           |                                                                               |                |          |

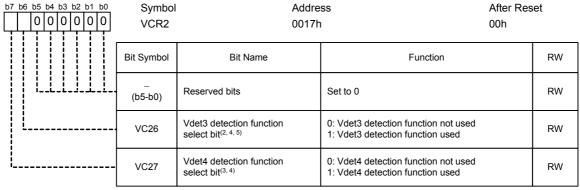

| 0017h                                                                                           | Voltage Detection Register 2                                                  | VCR2           | 52       |

| 0018h                                                                                           |                                                                               | _              | [        |

| 0019h                                                                                           | Address Match Interrupt Register 2                                            | RMAD2          | 127      |

| 001Ah                                                                                           |                                                                               |                |          |

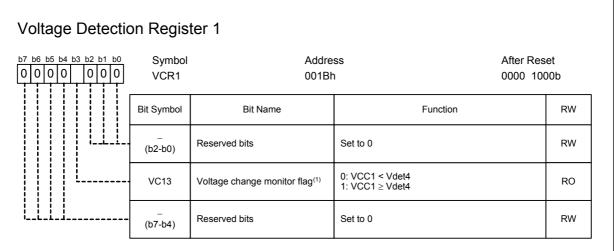

| 001Bh                                                                                           | Voltage Detection Register 1                                                  | VCR1           | 52       |

| 001Ch                                                                                           |                                                                               | 1              | I        |

| 001Dh                                                                                           | Address Match Interrupt Register 3                                            | RMAD3          | 127      |

| 001Eh                                                                                           |                                                                               |                |          |

| 001Fh                                                                                           |                                                                               |                |          |

| 0020h                                                                                           |                                                                               |                |          |

| 0021h                                                                                           |                                                                               |                |          |

| 0022h                                                                                           |                                                                               |                |          |

| 0023h                                                                                           |                                                                               |                |          |

| 0024h                                                                                           |                                                                               |                |          |

| 0025h                                                                                           |                                                                               |                |          |

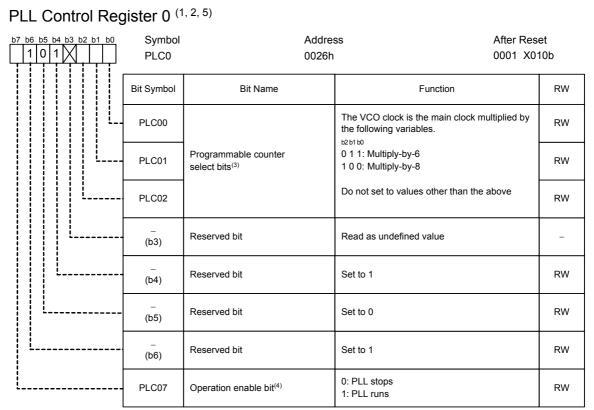

| 0026h                                                                                           | PLL Control Register 0                                                        | PLC0           | 86       |

| 0027h                                                                                           | PLL Control Register 1                                                        | PLC1           | 86       |

| 0028h                                                                                           |                                                                               |                |          |

| 0029h                                                                                           | Address Match Interrupt Register 4                                            | RMAD4          | 127      |

| 002Ah                                                                                           |                                                                               |                |          |

| 002Bh                                                                                           |                                                                               |                |          |

| 002Ch                                                                                           |                                                                               |                |          |

| 002Dh                                                                                           | Address Match Interrupt Register 5                                            | RAMD5          | 127      |

| 002Eh                                                                                           |                                                                               |                |          |

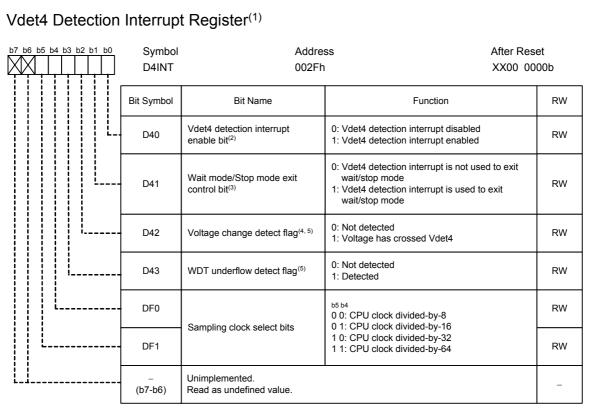

| 002Fh                                                                                           | Vdet4 Detection Interrupt Register                                            | D4INT          | 53       |

| 0030h                                                                                           |                                                                               |                |          |

| 0031h                                                                                           |                                                                               |                |          |

| 0032h                                                                                           |                                                                               |                |          |

| 0033h                                                                                           |                                                                               |                |          |

| 0034h                                                                                           |                                                                               |                |          |

| 0035h                                                                                           |                                                                               |                |          |

| 0036h                                                                                           |                                                                               |                |          |

| 0037h                                                                                           |                                                                               |                |          |

| 0038h                                                                                           | Address Metables 15 15 15                                                     | D              | 10-      |

| 0039h                                                                                           | Address Match Interrupt Register 6                                            | RMAD6          | 127      |

| 003Ah                                                                                           |                                                                               |                | <b>.</b> |

| 003Bh                                                                                           |                                                                               | +              | <u> </u> |

| 003Ch                                                                                           | Address Metableton (D. )                                                      | DM4.5-         | 467      |

| 003Dh                                                                                           | Address Match Interrupt Register 7                                            | RMAD7          | 127      |

| 003Eh                                                                                           |                                                                               |                | <u> </u> |

| 003Fh                                                                                           |                                                                               |                | 1        |

| 0040h                                                                                           |                                                                               |                |          |

| 00445                                                                                           |                                                                               |                |          |

| 0041h                                                                                           |                                                                               |                |          |

| 0042h                                                                                           |                                                                               |                |          |

| 0042h<br>0043h                                                                                  |                                                                               |                |          |

| 0042h<br>0043h<br>0044h                                                                         |                                                                               |                |          |

| 0042h<br>0043h<br>0044h<br>0045h                                                                |                                                                               |                |          |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h                                                       |                                                                               |                |          |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h                                              | External Cases Wait Casted Decistes 2                                         | EWCDA          | 60       |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h                                     | External Space Wait Control Register 0                                        | EWCRO          | 69       |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h                            | External Space Wait Control Register 1                                        | EWCR1          | 69       |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah                   | External Space Wait Control Register 1 External Space Wait Control Register 2 | EWCR1<br>EWCR2 | 69<br>69 |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah                   | External Space Wait Control Register 1                                        | EWCR1          | 69       |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh          | External Space Wait Control Register 1 External Space Wait Control Register 2 | EWCR1<br>EWCR2 | 69<br>69 |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch | External Space Wait Control Register 1 External Space Wait Control Register 2 | EWCR1<br>EWCR2 | 69<br>69 |

| 0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh          | External Space Wait Control Register 1 External Space Wait Control Register 2 | EWCR1<br>EWCR2 | 69<br>69 |

Blank spaces are reserved. No access is allowed.

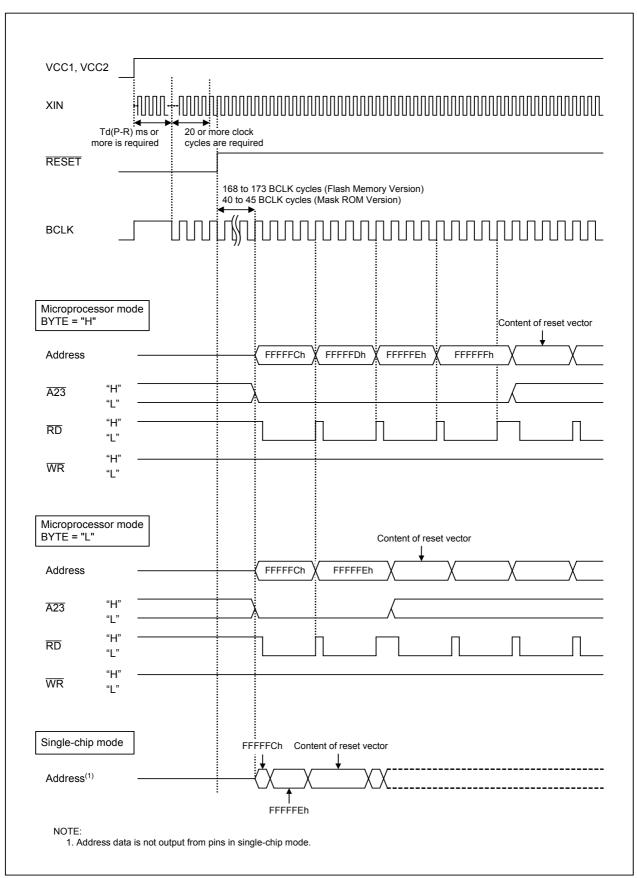

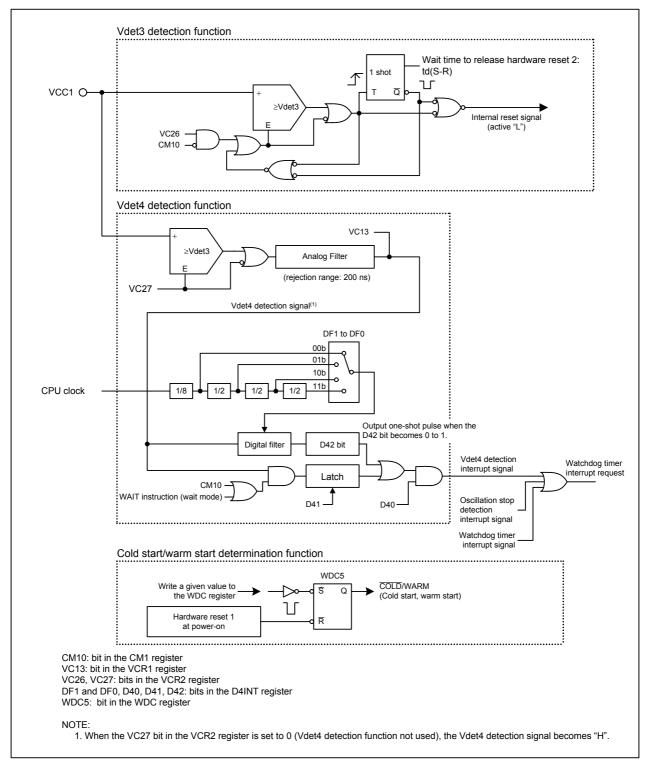

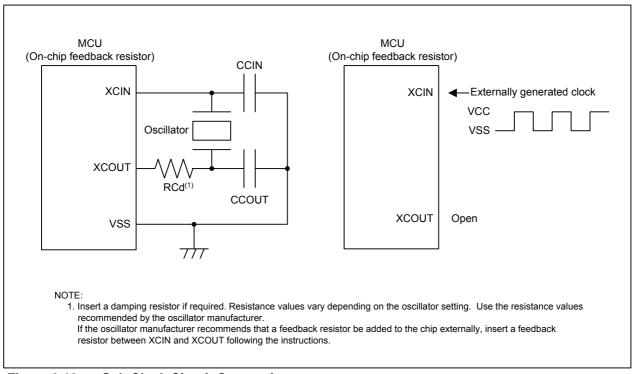

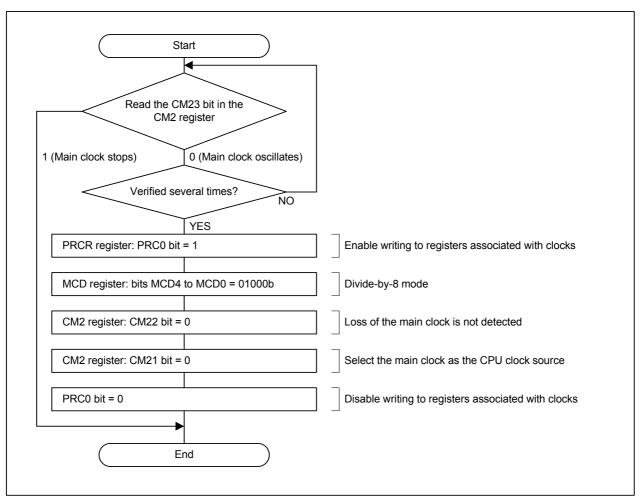

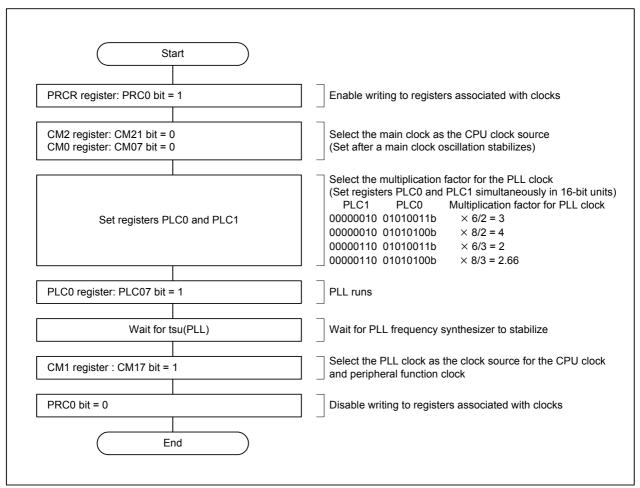

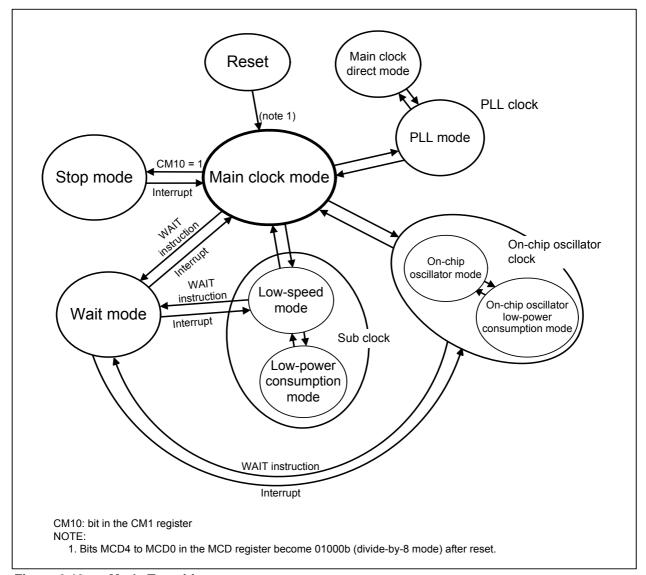

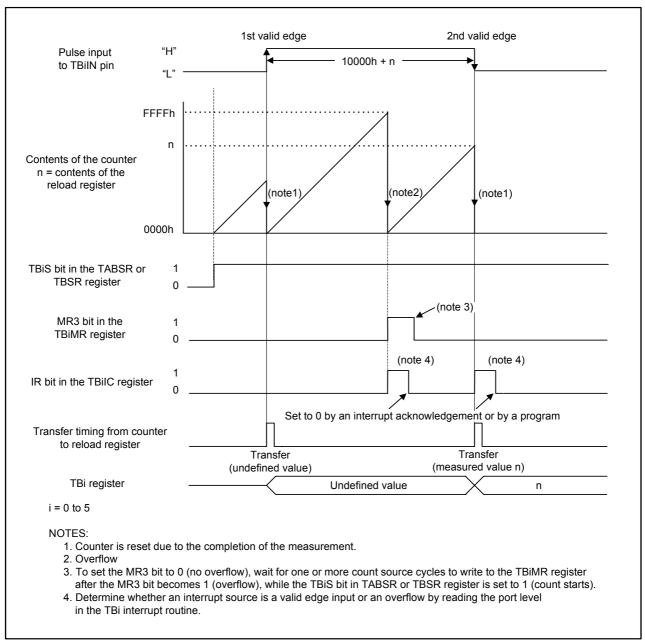

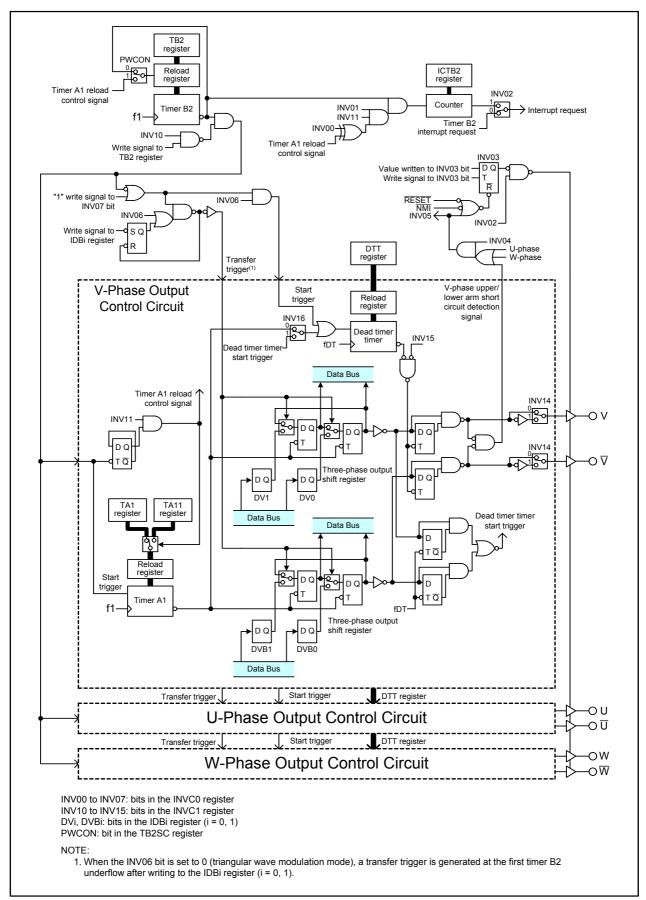

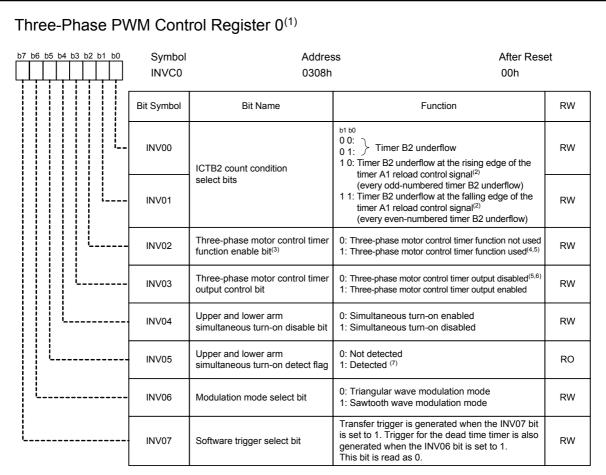

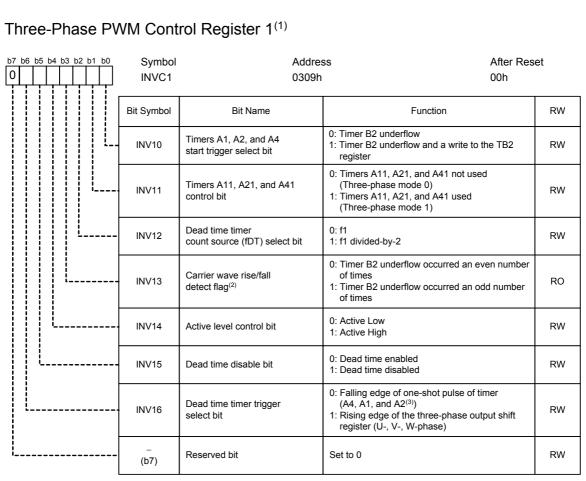

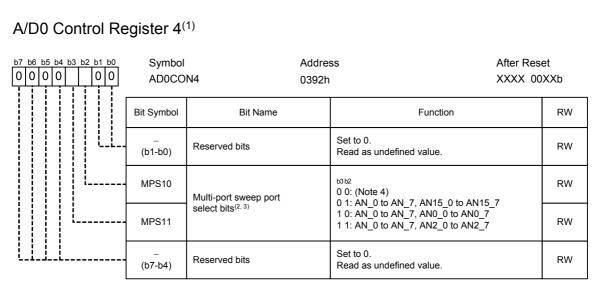

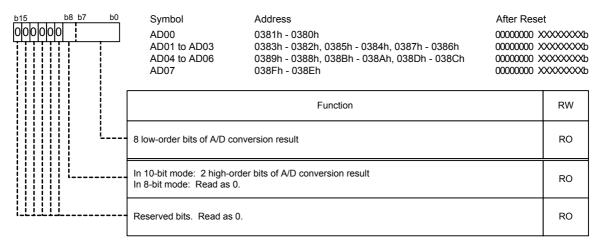

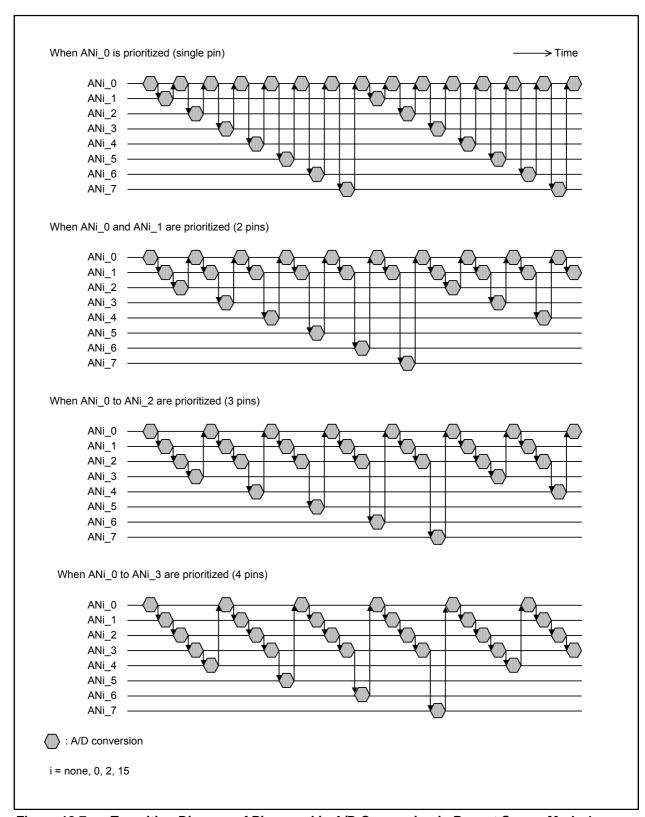

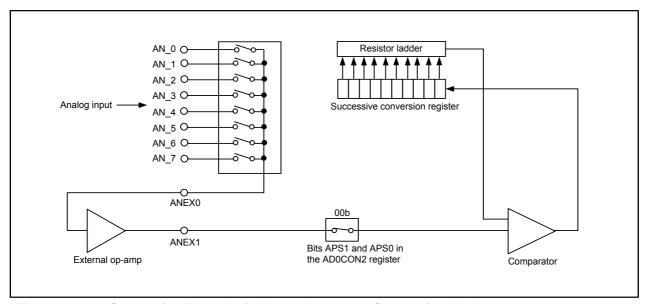

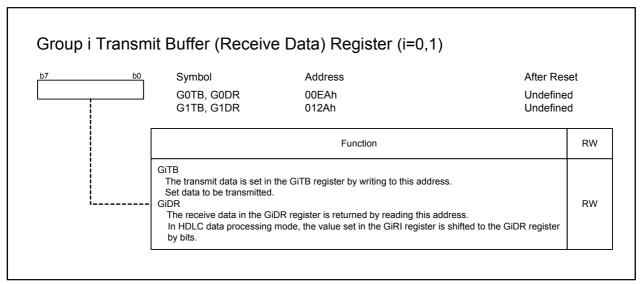

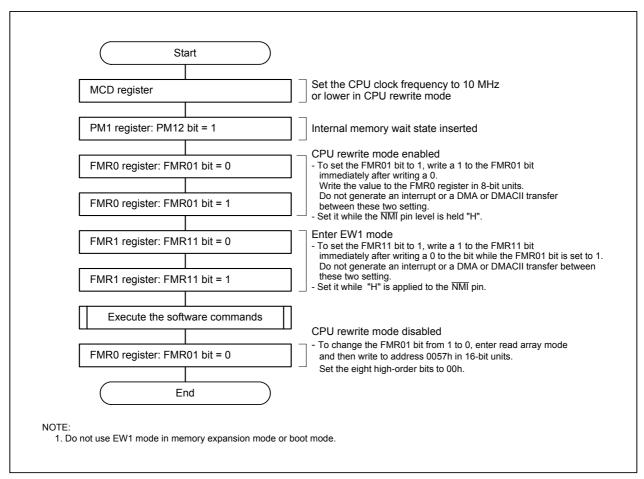

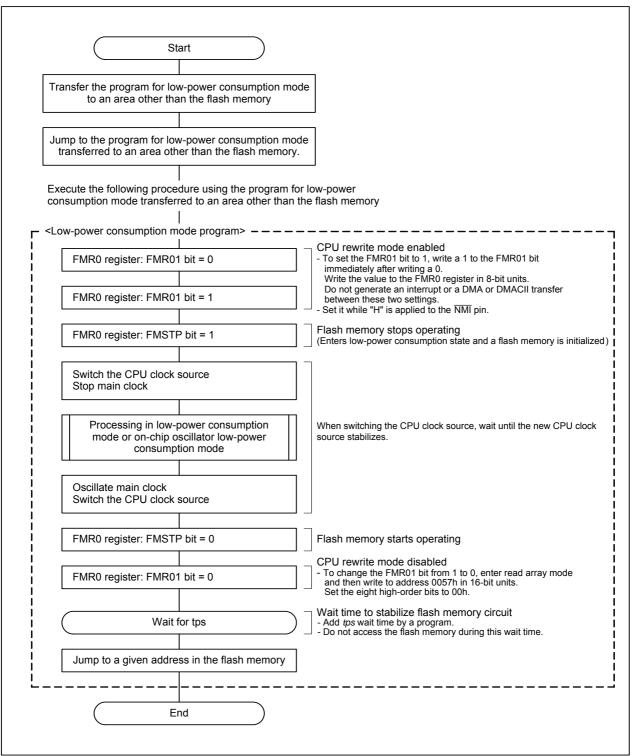

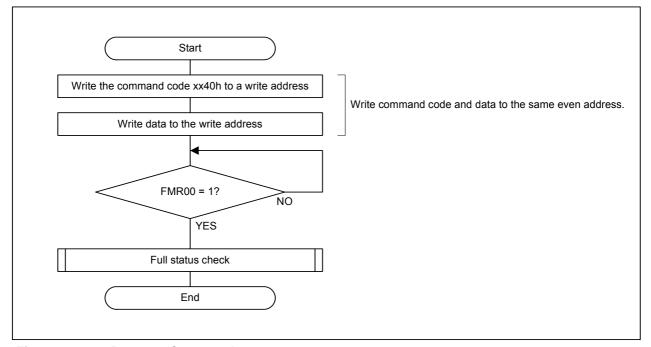

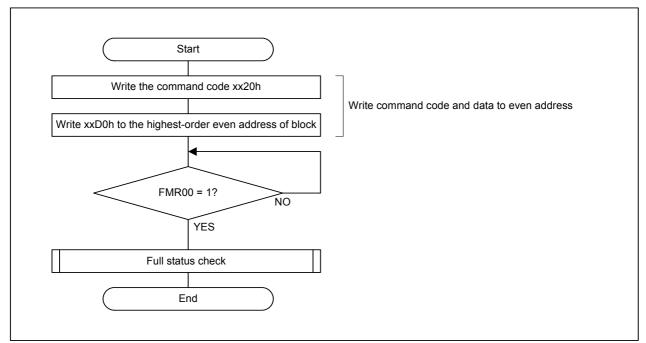

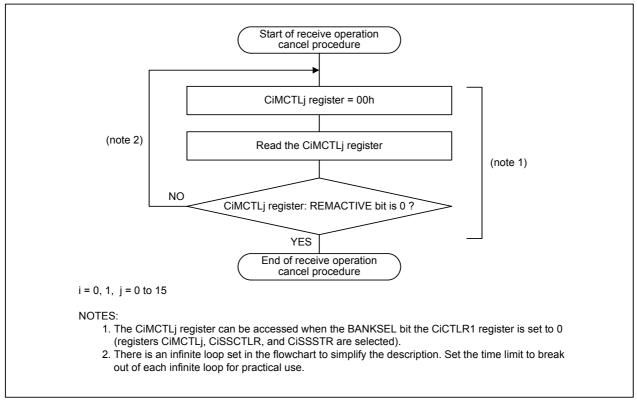

| Address                 | Register                                                                 | Symbol             | Page       |